**REINALDO SILVEIRA**

**DIRETRIZES PARA UMA NOVA

METODOLOGIA DE PROJETO DIGITAL**

Tese apresentada à Escola

Politécnica da Universidade de

São Paulo para obtenção de Título

de Doutor em Engenharia Elétrica.

São Paulo

2004

Deixada em Branco

**REINALDO SILVEIRA**

**DIRETRIZES PARA UMA NOVA

METODOLOGIA DE PROJETO DIGITAL**

Tese apresentada à Escola

Politécnica da Universidade de

São Paulo para obtenção do Título

de Doutor em Engenharia Elétrica.

Área de Concentração:

Microeletrônica

Orientador: Prof. Titular

Wilhelmus A. M. Van Noije

São Paulo

2004

## FICHA CATALOGRÁFICA

**Silveira, Reinaldo**

**Diretrizes para uma nova metodologia de projeto Digital

/ Reinaldo Silveira – São Paulo, 2004.**

**212 p.**

**Tese (Doutorado) – Escola Politécnica da Universidade

de São Paulo. Departamento de Engenharia de Sistemas

Eletrônicos.**

**1. CAD (ferramentas) 2. Circuitos Integrados VLSI

3. Arquitetura e organização de computadores I. Universidade

de São Paulo. Escola Politécnica. Departamento de

Engenharia de Sistemas Eletrônicos II. t**

*Gostaria de dedicar este trabalho

aos meus parentes e amigos que

souberam me apoiar e incentivar

durante todo esse período.*

Deixada em Branco

# Agradecimentos

Ao Prof. Wilhelmus A. M. Van Noije pela valiosa orientação e apoio recebidos durante a realização do trabalho, e por acreditar na sua viabilidade, mesmo sabendo que a sua realização poderia avançar por campos de conhecimento novos para nós dois.

Ao amigo e colega Jecel Assumpção por me apresentar a linguagem SELF e por me orientar nos primeiros passos da programação orientada a objetos, Smalltalk e SELF.

Ao Conselho Nacional de Desenvolvimento Científico e Tecnológico (CNPq), pela bolsa de estudos que possibilitou a manutenção e o término deste trabalho nos últimos três anos.

A minha amiga Profa. Noely Ielo de Campos, por seus valiosos conselhos sobre estilo de redação e revisão do trabalho. Ao colega e amigo Gustavo Adolfo Cerezo Vásquez pelas também valiosas sugestões e ajudas recebidas.

E a todos os colegas e Professores da Poli (em especial do LSI), com os quais convivi por um bom tempo e ajudaram na minha formação básica de pesquisa que culminaram na realização deste trabalho.

Meus sinceros agradecimentos.

Deixada em Branco

# Resumo

Este trabalho apresenta uma nova metodologia de projeto digital, chamada “Metodologia Orientada ao Projetista”, ou simplesmente DO (“*Designer Oriented*”). A metodologia DO procura basicamente eliminar, do fluxo de projeto, conceitos e operações estranhas ao domínio de aplicação. Isso é feito através do uso de ferramentas computacionais especialmente projetadas cujo modo de operação procura favorecer o usuário (projetista de *hardware*), de forma a ser sempre a mais intuitiva possível e se adaptar às suas necessidades. Dessa forma, procuramos transformar a tarefa de projeto em algo mais acessível, exigindo menos treinamento específico, diminuindo consequentemente os custos associados ao mesmo.

Para demonstrar a metodologia, propomos o sistema SELFHDL que é um sistema de descrição de *hardware* implementado na linguagem SELF. Sistema que utiliza recursos gráficos e textuais para elaborar a descrição de um sistema digital. Descrição essa extremamente simples de ser compreendida permitindo que seja utilizada também como sistema didático de auxílio ao ensino de sistemas digitais. O sistema descrito pode também ser simulado de forma interativa através de um ambiente virtual no qual o próprio sistema descrito é emulado, podendo interagir com o usuário ou com o ambiente computacional que o circunda como se o *hardware* descrito efetivamente existisse. Por ser implementado em SELF, o sistema SELFHDL não precisa ser compilado, sendo que qualquer modificação tem efeito imediato como se fosse um sistema interpretado. Este trabalho apresenta a implementação do SELFHDL e a sua utilização através de um projeto-exemplo.

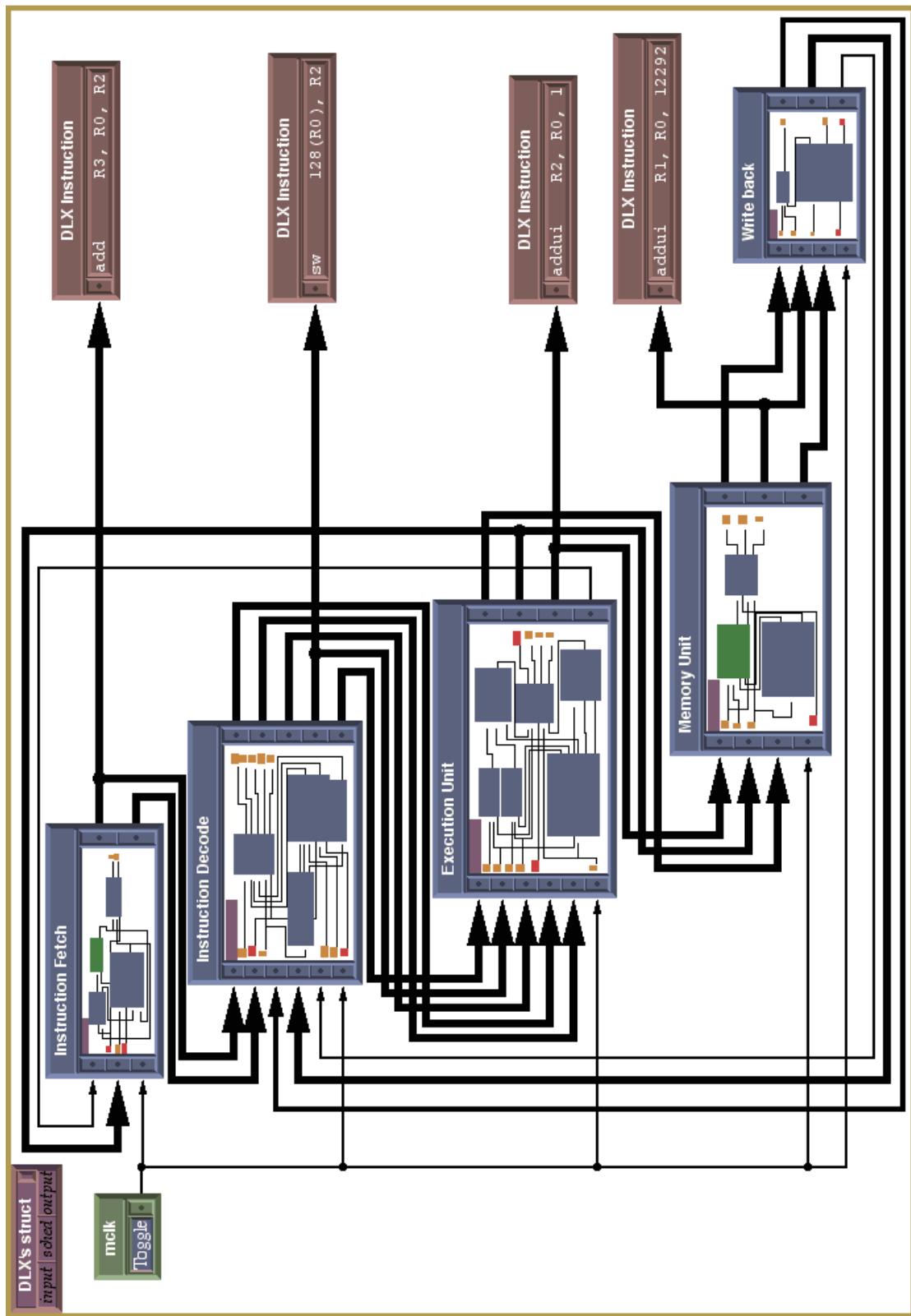

A implementação em SELFHDL da arquitetura DLX é utilizada como projeto-exemplo. Nele podemos comparar uma implementação tradicional feita em VHDL com a descrição SELFHDL e constatar na prática as vantagens do novo sistema. Veremos que essa nova forma é muito intuitiva para o projetista, normalmente acostumado a lidar com representações e modelos gráficos dos elementos do seu domínio e cujo espírito é normalmente educado em experimentação e manipulação. O sistema SELFHDL é um ambiente propício para que os projetistas possam avaliar diversas alternativas para os seus projetos em desenvolvimento. Finalmente, concluímos o trabalho falando das potencialidades do sistema e dos trabalhos futuros aos quais pensamos nos dedicar ou ainda orientá-los como linhas de pesquisa a fim de ampliar o sistema e torná-lo mais poderoso.

# Abstract

This work presents a new methodology for digital design, called “Designer Oriented Methodology” (DO). The main idea behind the DO methodology is to make the computational tools closer to the domain of application. This is done by eliminating, from the design flow, tasks and concepts strange or superfluous to the final user. This methodology uses especially designed computer tools to avoid or hide unwanted aspects of the design from the user (*hardware* designer), The design process should interact with the system in a way that the designer’s attention should be totally focused on the subject of his/hers work, as much as possible. Like a player and his game are involved and absorbed by the reality of the game.

To demonstrate the methodology, it is presented the system **SELFHDL** which is a hardware description language written in the programming language **SELF**. **SELFHDL** uses graphical and textual elements to elaborate a description of a digital system, that is extremely simple to be understood allowing its use as didactic support system for the education aid of digital systems. The described system can also be simulated in interactive mode, through a virtual environment where the described system is emulated, being able to interact with the user or the computer environment that surrounds it, as the real hardware would. Being implemented in **SELF**, means that the **SELFHDL** system does not need to be compiled, so any modification has immediate effect as if the system were interpreted. This work presents the implementation of **SELFHDL** and its use in an example project.

The **SELFHDL** implementation of the DLX architecture is used as the example project. We compare two traditional DLX designs made in VHDL with the **SELFHDL** description and discuss the the advantages of the new system. We will see that this new form is very intuitive for designers, normally used to deal with graphic models of the elements of their domain and whose spirit normally is educated in experimentation and manipulation. The **SELFHDL** system is a propitious environment where the designers can evaluate many alternatives for their projects under development. Finally, we conclude the work speaking of the potentialities of the new system and the future works we intend to dedicate or advise as a new research field in order to extend the system and to make it more powerful.

# Conteúdo

|          |                                                                         |           |

|----------|-------------------------------------------------------------------------|-----------|

| <b>1</b> | <b>INTRODUÇÃO</b>                                                       | <b>1</b>  |

| 1.1      | Justificativa e Motivações . . . . .                                    | 3         |

| 1.2      | Objetivos . . . . .                                                     | 5         |

| 1.3      | Convenções . . . . .                                                    | 6         |

| 1.4      | Organização da Tese . . . . .                                           | 7         |

| <b>2</b> | <b>ESTADO DA ARTE</b>                                                   | <b>9</b>  |

| 2.1      | Estado da Arte em Ferramentas de Projeto Digital . . . . .              | 9         |

| 2.1.1    | Compilação de Silício . . . . .                                         | 13        |

| 2.1.2    | Síntese de Alto Nível . . . . .                                         | 21        |

| 2.1.3    | Linguagens de Descrição de <i>Hardware</i> . . . . .                    | 27        |

| 2.1.4    | Verificação Formal . . . . .                                            | 34        |

| 2.1.5    | Especificação de Sistemas e <i>Hardware/Software Codesign</i> . . . . . | 37        |

| 2.2      | Linguagem de Programação SELF . . . . .                                 | 45        |

| 2.2.1    | Histórico . . . . .                                                     | 45        |

| 2.2.2    | Princípios Básicos da Linguagem . . . . .                               | 47        |

| 2.2.3    | A linguagem . . . . .                                                   | 49        |

| 2.2.4    | <i>Run Time Environment</i> . . . . .                                   | 56        |

| 2.2.5    | Interface Gráfica do Usuário . . . . .                                  | 58        |

| 2.3      | Conclusões . . . . .                                                    | 66        |

| <b>3</b> | <b>METODOLOGIA</b>                                                      | <b>67</b> |

| 3.1      | Linguagens de Programação . . . . .                                     | 68        |

| 3.1.1    | Desenvolvimento em SELF . . . . .                                       | 72        |

---

|          |                                                              |            |

|----------|--------------------------------------------------------------|------------|

| 3.1.2    | Conclusão                                                    | 75         |

| 3.2      | Aplicação Orientada ao Usuário                               | 76         |

| 3.3      | Ferramentas de Desenvolvimento de Sistemas Digitais          | 77         |

| 3.4      | Desenvolvimento Orientado ao Projetista                      | 80         |

| 3.5      | Conceito de Jogo no Desenvolvimento                          | 83         |

| 3.6      | Implementação                                                | 85         |

| <b>4</b> | <b>SELFHDL</b>                                               | <b>91</b>  |

| 4.1      | Metodologia Orientada ao Projetista e SELFHDL                | 91         |

| 4.2      | <i>Hardware Description Language</i> em SELF                 | 93         |

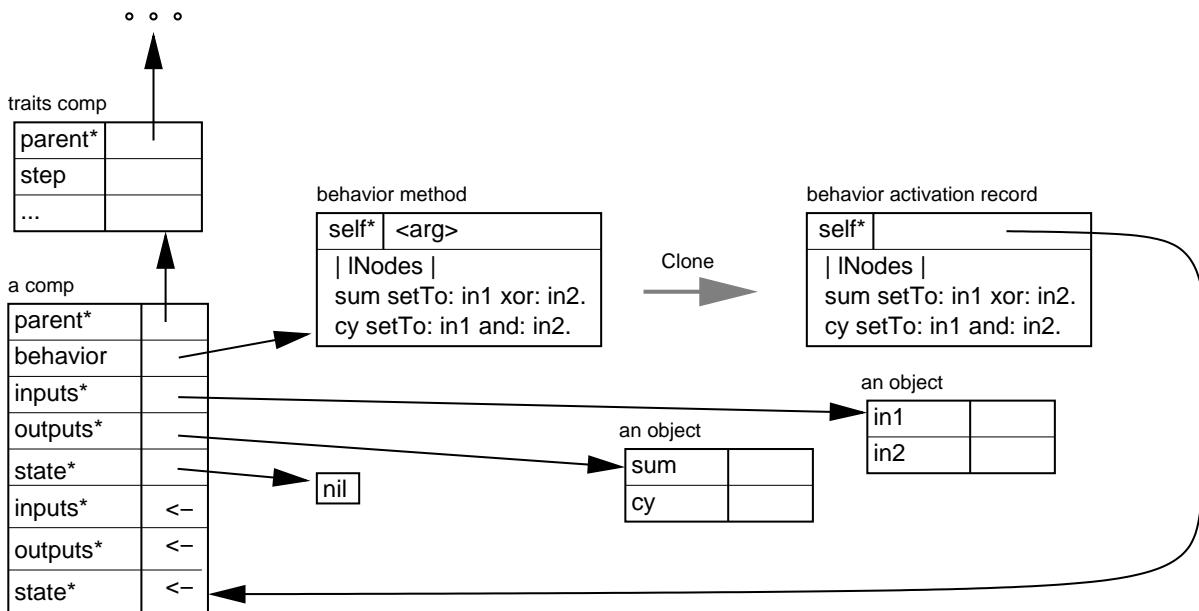

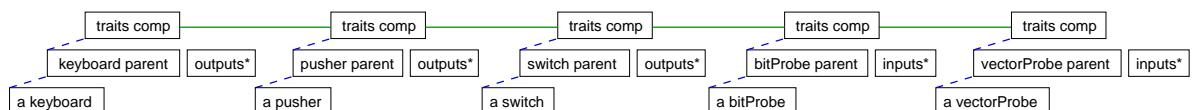

| 4.2.1    | O objeto <code>comp</code>                                   | 94         |

| 4.2.2    | O objeto <code>node</code>                                   | 96         |

| 4.2.3    | O objeto <code>nodeVector</code>                             | 97         |

| 4.2.4    | O objeto <code>connection</code>                             | 98         |

| 4.2.5    | O objeto <code>schedulerMorph</code>                         | 99         |

| 4.2.6    | O objeto <code>sComp</code>                                  | 101        |

| 4.3      | Hierarquia e Dinâmica entre os Objetos                       | 102        |

| 4.3.1    | Hierarquia de Objetos                                        | 103        |

| 4.3.2    | Dinâmica da simulação                                        | 112        |

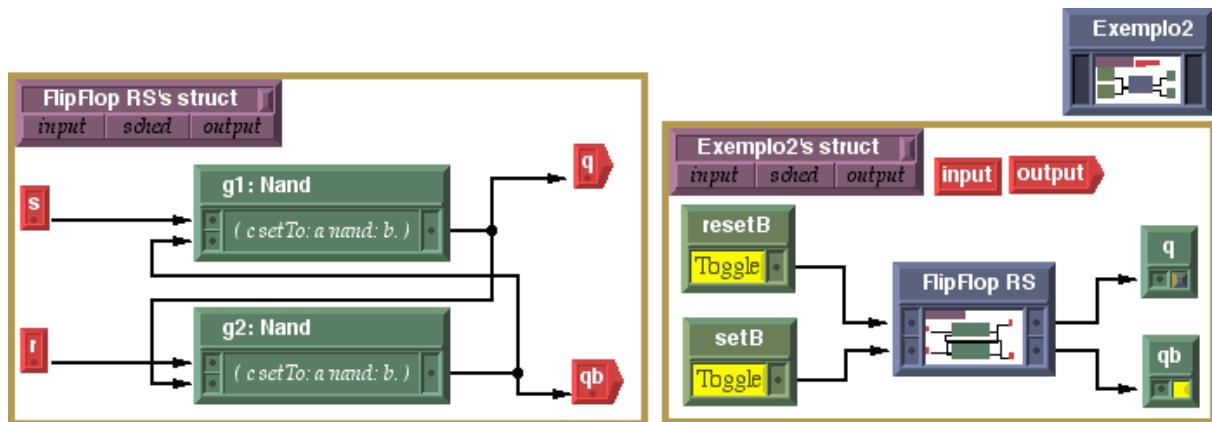

| 4.4      | Descrição e Simulação                                        | 118        |

| 4.4.1    | Combinatório e Seqüencial                                    | 119        |

| 4.4.2    | Simulação Interativa                                         | 120        |

| 4.5      | Conclusão                                                    | 121        |

| <b>5</b> | <b>UTILIZANDO O SELFHDL</b>                                  | <b>123</b> |

| 5.1      | Regras e sugestões para uma boa descrição de <i>hardware</i> | 123        |

| 5.1.1    | Biblioteca de Células                                        | 124        |

| 5.1.2    | Transferência de Dados                                       | 124        |

| 5.1.3    | Entradas e Saídas Registradas                                | 124        |

| 5.1.4    | Nomeação de Sinais e Componentes                             | 125        |

| 5.1.5    | Não uso de <i>Tri-States</i>                                 | 126        |

| 5.1.6    | Simplificação de Operações Complexas                         | 127        |

---

|       |                                                  |     |

|-------|--------------------------------------------------|-----|

| 5.1.7 | Circuitos Auxiliares e de Teste                  | 127 |

| 5.2   | Dicas e convenções para uso de SELFHDL           | 128 |

| 5.2.1 | Organizando um projeto                           | 128 |

| 5.2.2 | Convenções da codificação de Blocos              | 130 |

| 5.2.3 | Desenho dos circuitos                            | 130 |

| 5.3   | Implementação de componentes especiais           | 132 |

| 5.3.1 | Observadores                                     | 132 |

| 5.3.2 | Estimuladores                                    | 134 |

| 5.3.3 | Outros Componentes                               | 136 |

| 5.4   | Projeto Exemplo: Processador DLX                 | 139 |

| 5.4.1 | Arquitetura DLX                                  | 140 |

| 5.4.2 | Primeiro estágio de <i>pipeline</i>              | 143 |

| 5.4.3 | Segundo estágio de <i>pipeline</i>               | 144 |

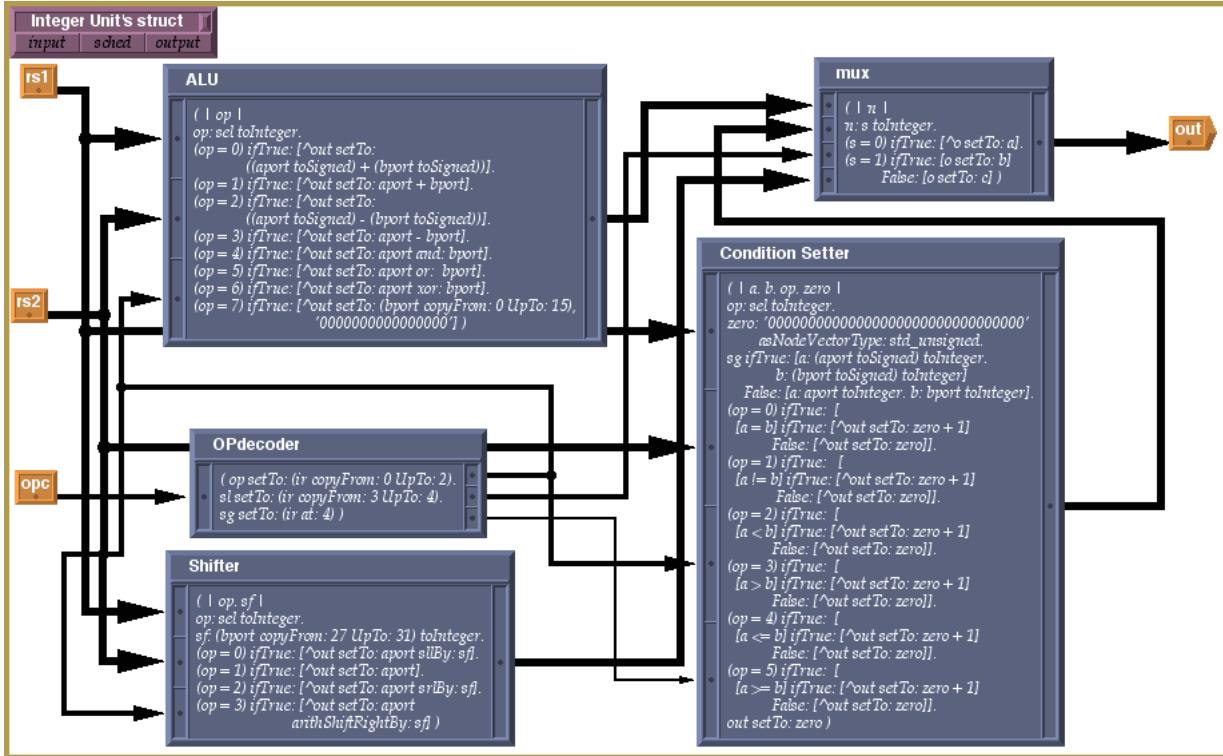

| 5.4.4 | Terceiro estágio de <i>pipeline</i>              | 146 |

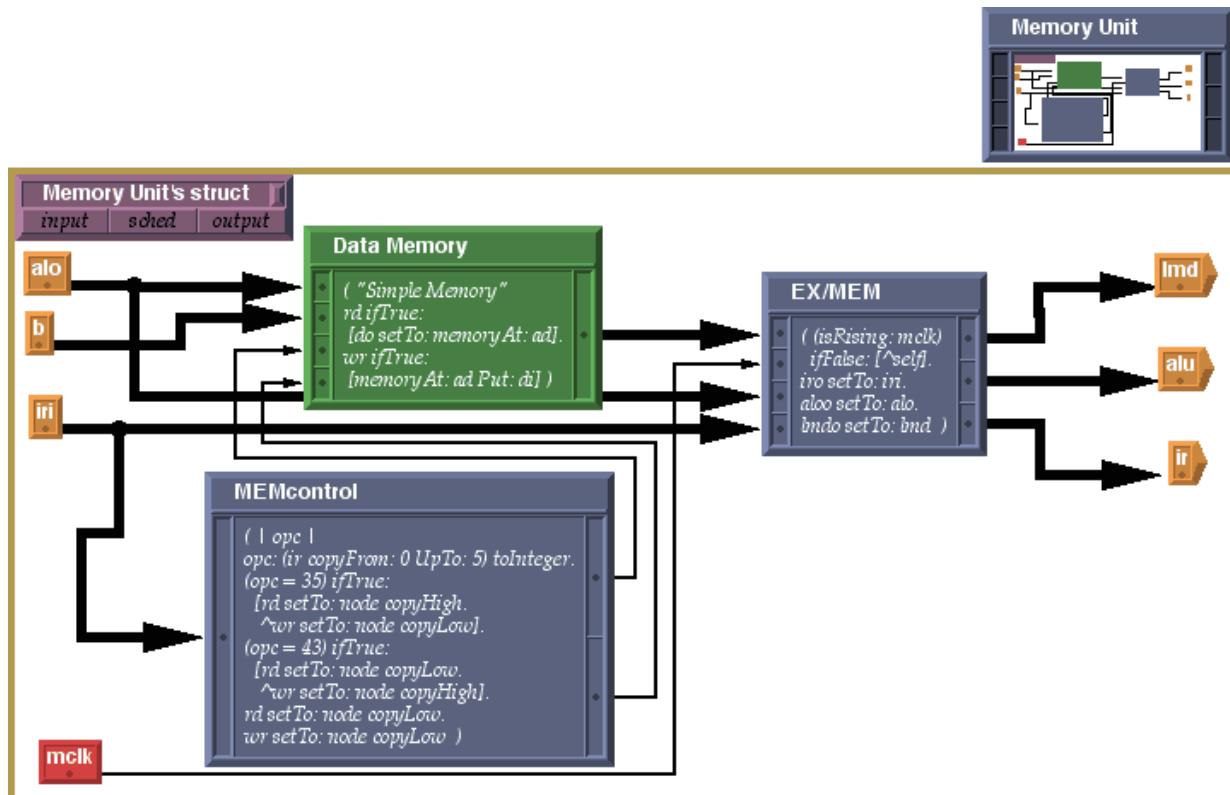

| 5.4.5 | Quarto estágio de <i>pipeline</i>                | 149 |

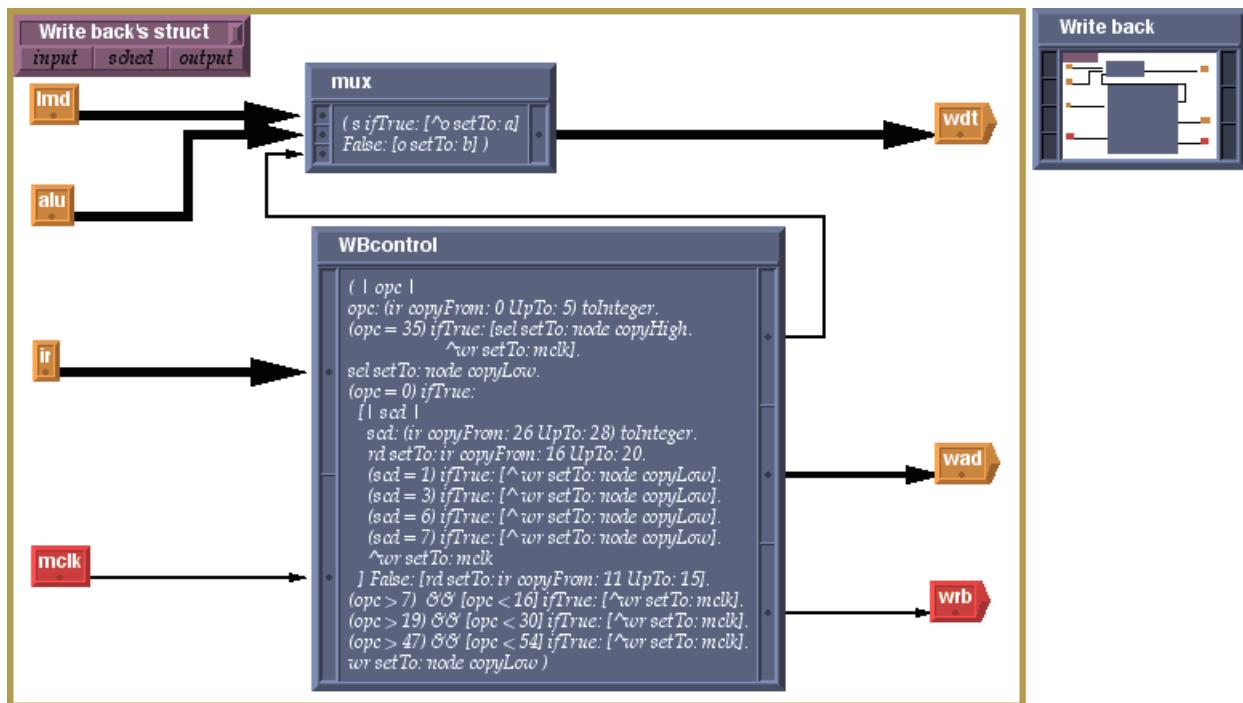

| 5.4.6 | Quinto estágio de <i>pipeline</i>                | 150 |

| 5.4.7 | Avaliação da Implementação                       | 151 |

| 5.5   | Conclusão                                        | 153 |

| 6     | CONCLUSÕES E MOTIVAÇÕES FUTURAS                  | 155 |

| 6.1   | Desvantagens do sistema SELFHDL                  | 157 |

| 6.2   | Motivações Futuras                               | 158 |

| A     | INSTRUÇÕES DA ARQUITETURA DLX                    | 161 |

| A.1   | Instruções DLX                                   | 161 |

| A.2   | Formato de Instruções do DLX                     | 164 |

| B     | IMPLEMENTAÇÕES VHDL DA ARQUITETURA DLX           | 165 |

| B.1   | Implementação RTL da Arquitetura DLX             | 166 |

| B.1.1 | Implementação RTL do DLX                         | 166 |

| B.1.2 | Controlador                                      | 167 |

| B.2   | Implementação <i>Pipeline</i> da Arquitetura DLX | 172 |

|          |                                          |            |

|----------|------------------------------------------|------------|

| B.2.1    | Estágio de Busca de instrução            | 172        |

| B.2.2    | Estágio de Decodificação                 | 172        |

| B.2.3    | Estágio de Execução                      | 175        |

| B.2.4    | Estágio de Acesso a Memória              | 176        |

| B.2.5    | Integração dos Blocos                    | 178        |

| <b>C</b> | <b>PROGRAMAS DE TESTE DO DLX EXEMPLO</b> | <b>181</b> |

| C.1      | Programa Exemplo                         | 182        |

| C.2      | Programa Compilado                       | 182        |

# Listas de Figuras

|      |                                                                                                                      |    |

|------|----------------------------------------------------------------------------------------------------------------------|----|

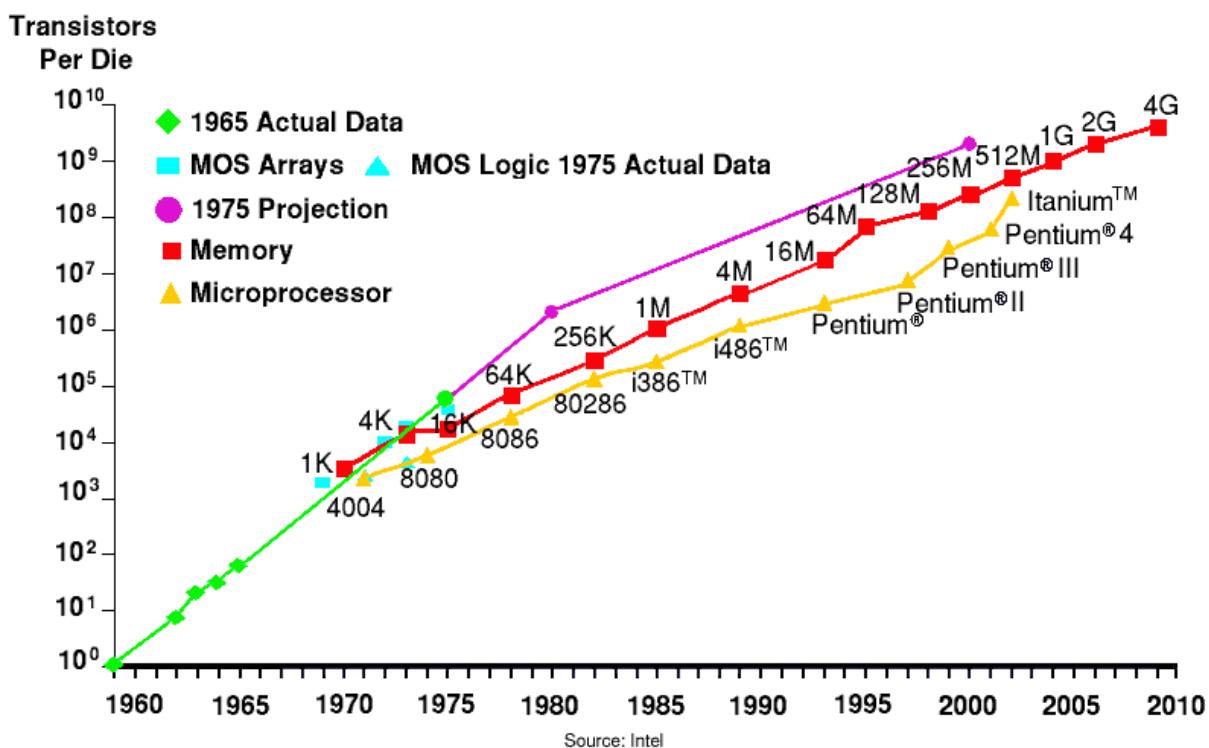

| 2.1  | Lei de Moore de acordo com a linha de processadores Intel. . . . .                                                   | 10 |

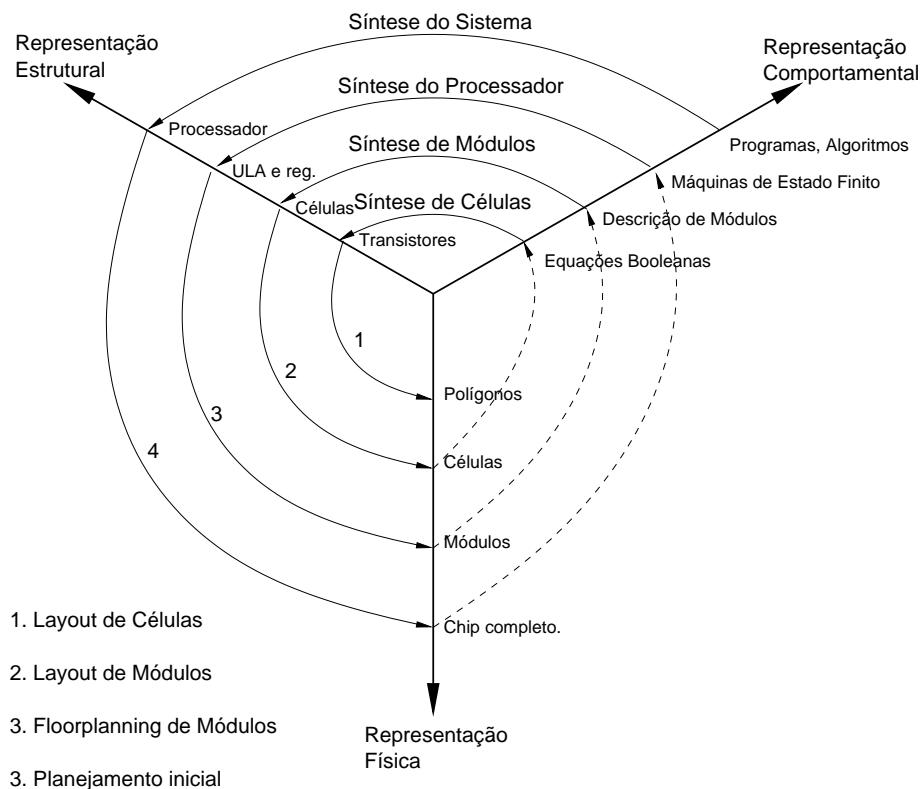

| 2.2  | Diagrama em Y. . . . .                                                                                               | 14 |

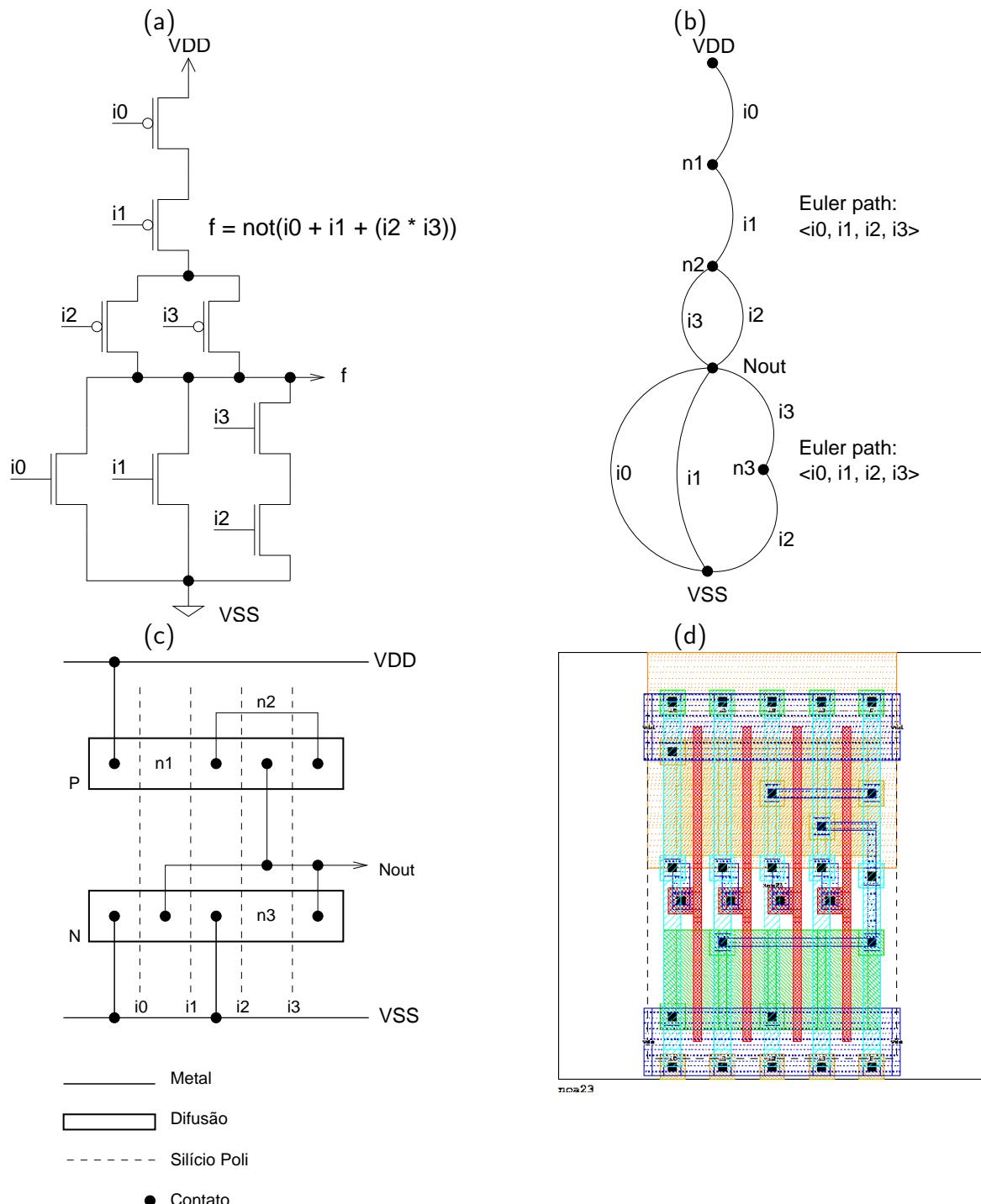

| 2.3  | Exemplo de síntese de células CMOS. . . . .                                                                          | 15 |

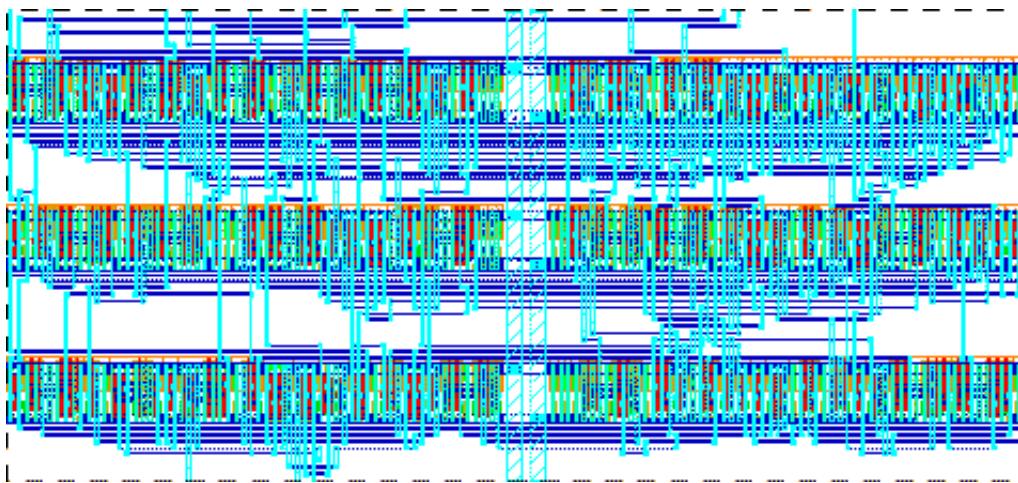

| 2.4  | Exemplo de implementação de lógica aleatória em <i>standard cells</i> . . . . .                                      | 17 |

| 2.5  | Exemplo de módulo regular, somador de 8 bits. . . . .                                                                | 17 |

| 2.6  | Modelo de Elementos de Processamento, PEs. . . . .                                                                   | 19 |

| 2.7  | Projeto de sistemas baseados em Compilação de Silício. . . . .                                                       | 20 |

| 2.8  | <i>Control and Data Flow Graphs</i> . . . . .                                                                        | 23 |

| 2.9  | Fluxo de Projeto usando Verificação Formal. . . . .                                                                  | 36 |

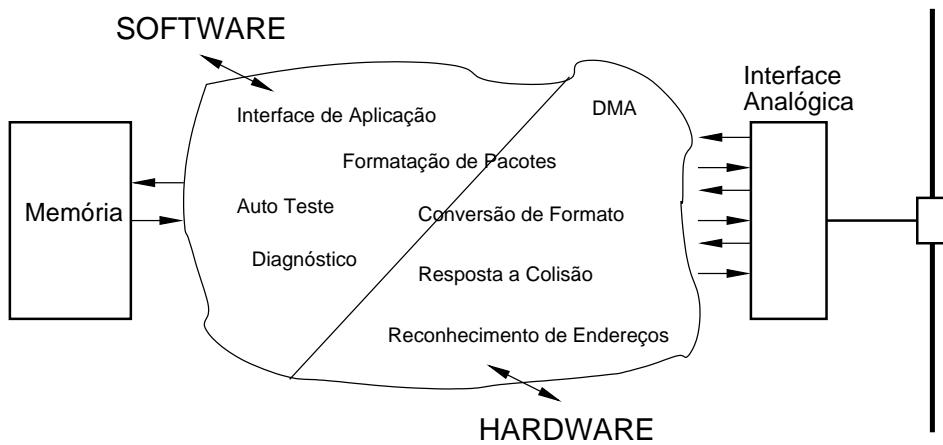

| 2.10 | Especificação de um sistema envolvendo <i>hardware</i> e <i>software</i> . . . . .                                   | 44 |

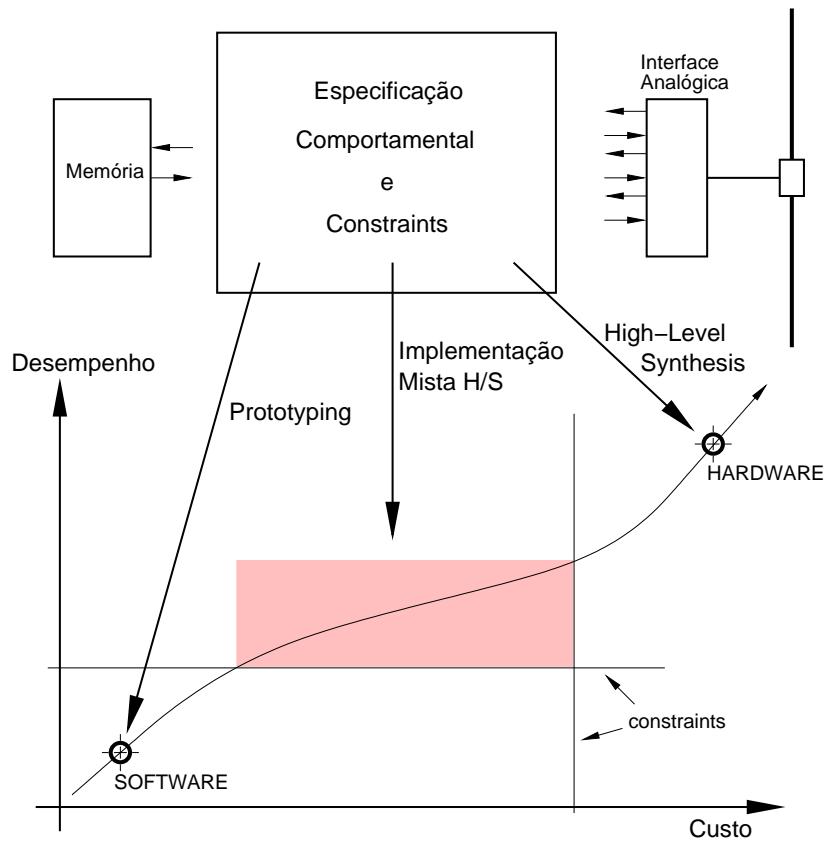

| 2.11 | Objetivos do <i>Hardware/Software Co-design</i> . . . . .                                                            | 45 |

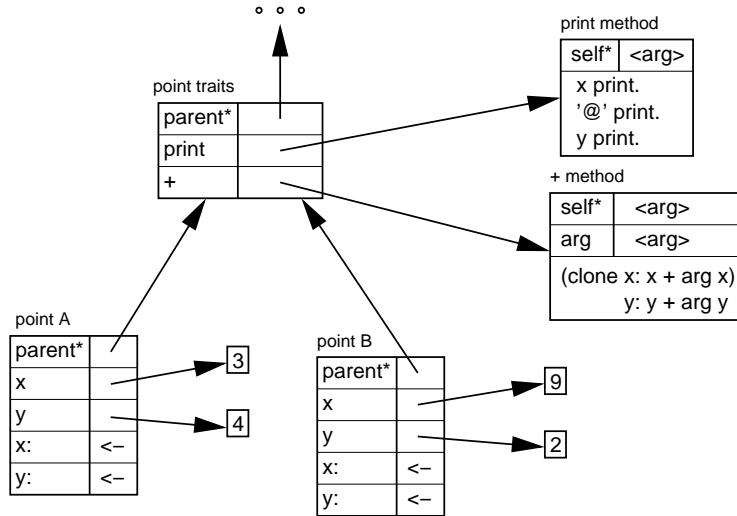

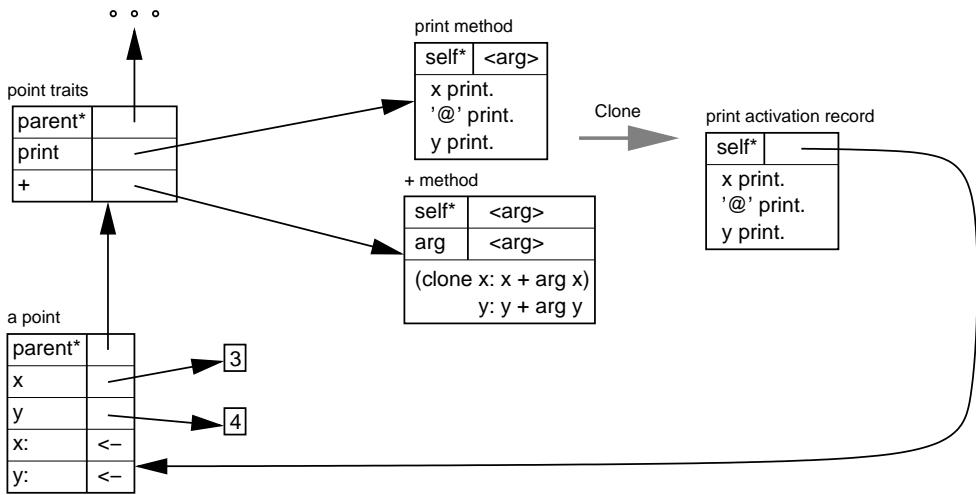

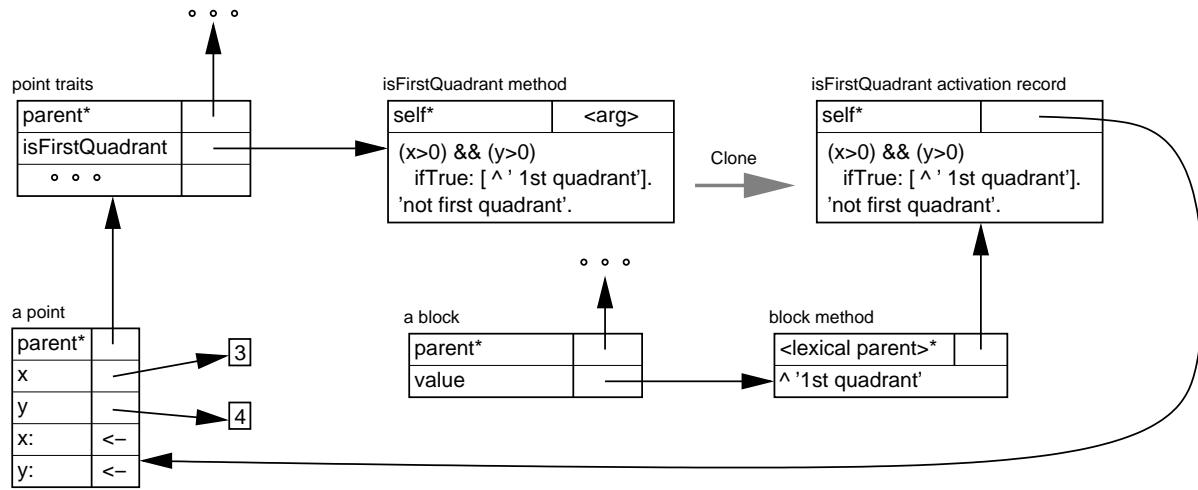

| 2.12 | Modelo de objetos do SELF. . . . .                                                                                   | 50 |

| 2.13 | Avaliação de mensagens em SELF. . . . .                                                                              | 52 |

| 2.14 | Usando blocos para criar estruturas de controle. . . . .                                                             | 54 |

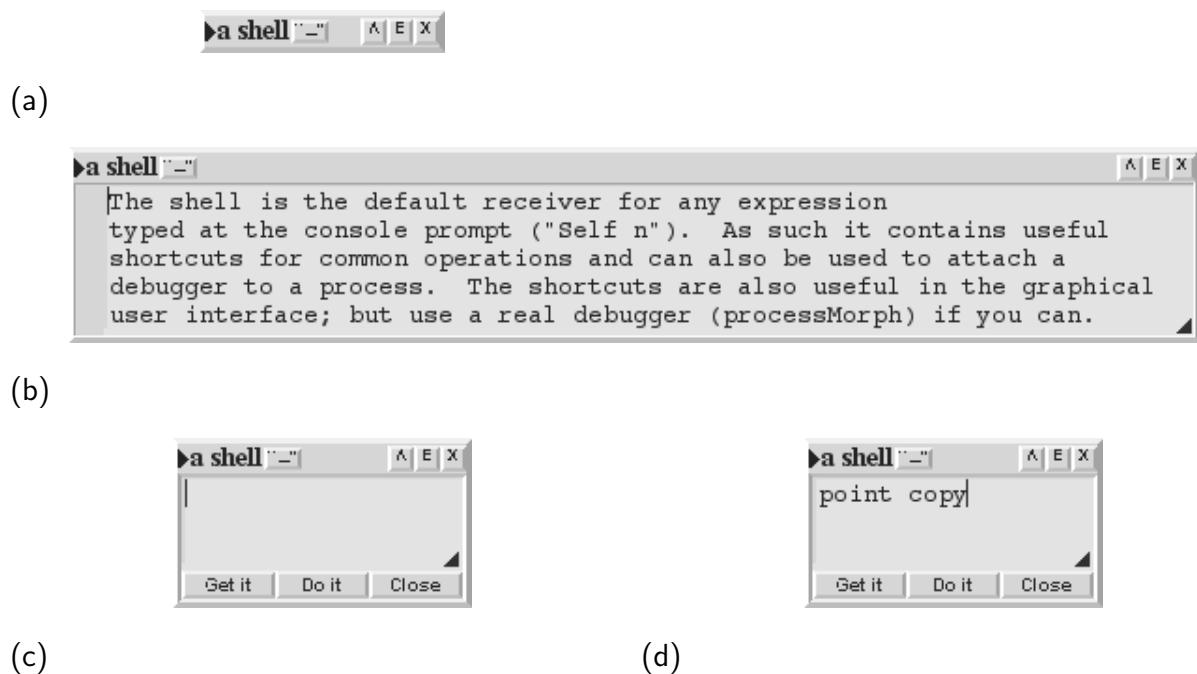

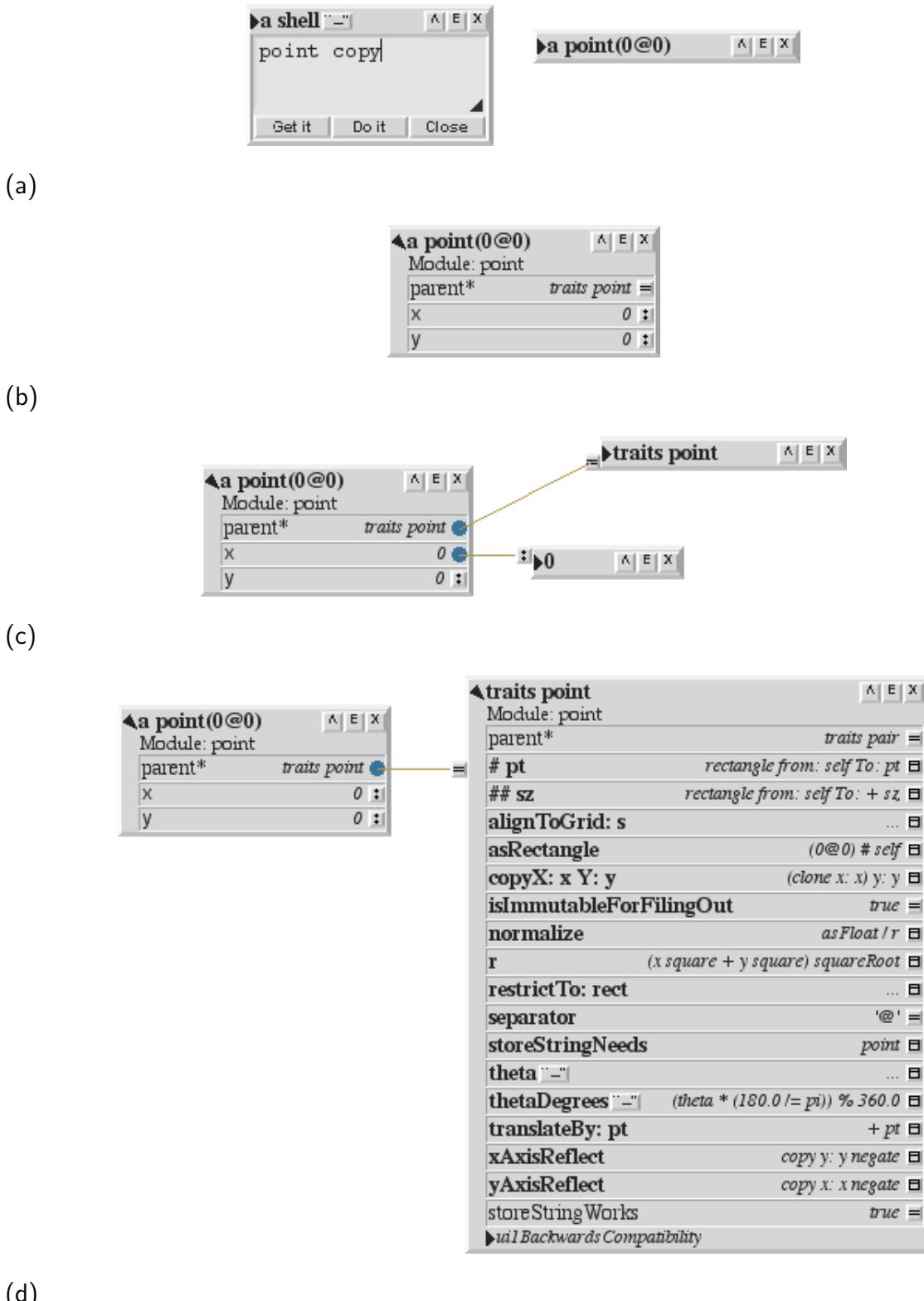

| 2.15 | Exemplo de objetos Self. . . . .                                                                                     | 59 |

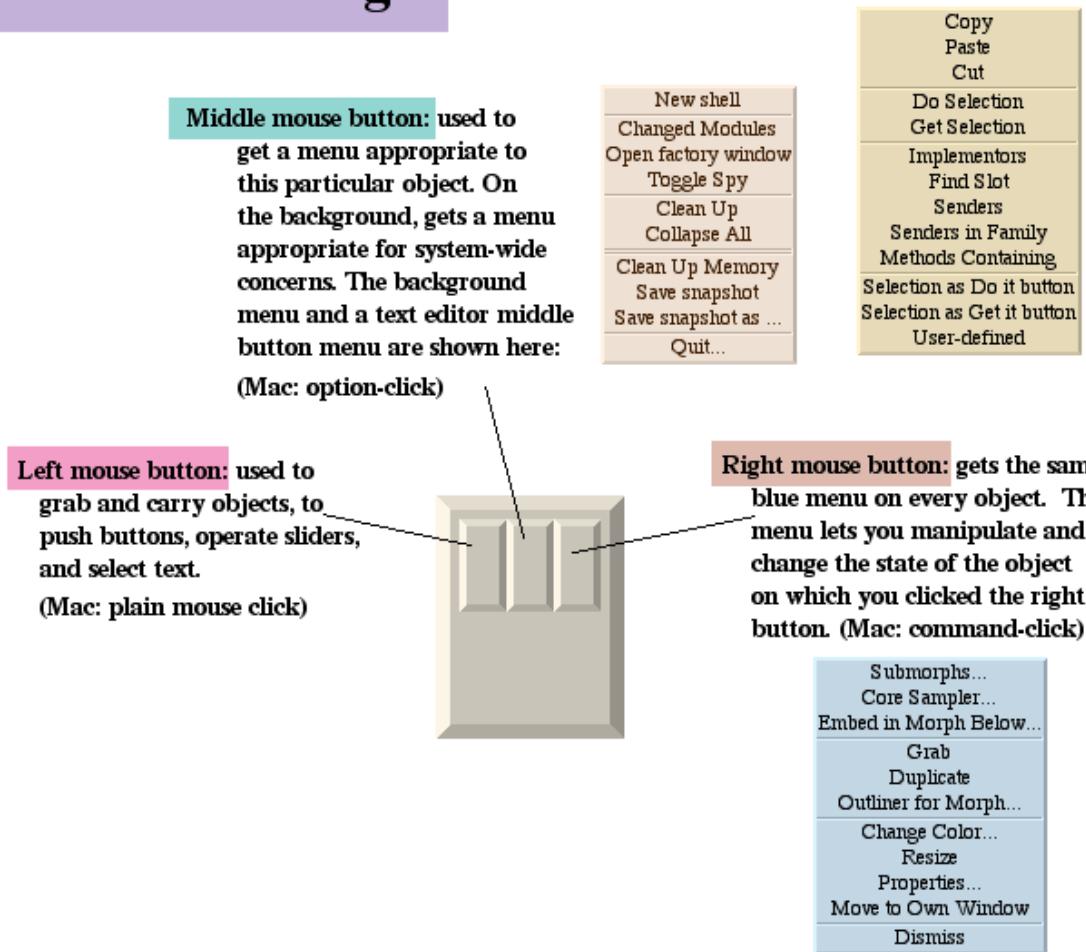

| 2.16 | Funções do <i>mouse</i> no ambiente gráfico do Self. . . . .                                                         | 61 |

| 2.17 | Criando e examinando o objeto a <i>point</i> . . . . .                                                               | 62 |

| 3.1  | Aproximação Homem-Máquina através das linguagens de programação. . . . .                                             | 68 |

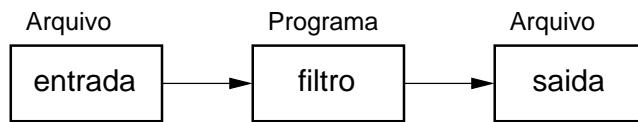

| 3.2  | Esquema tradicional de operação de programas. . . . .                                                                | 81 |

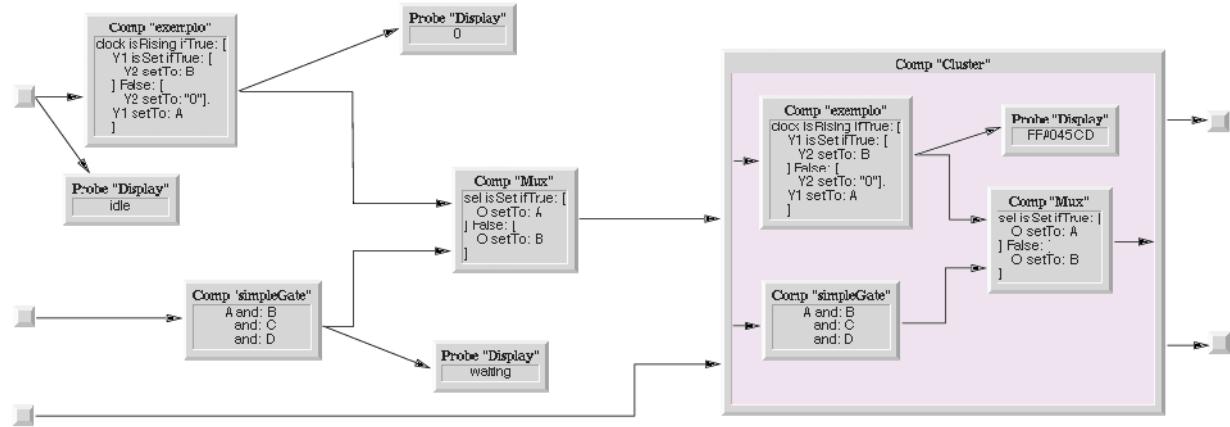

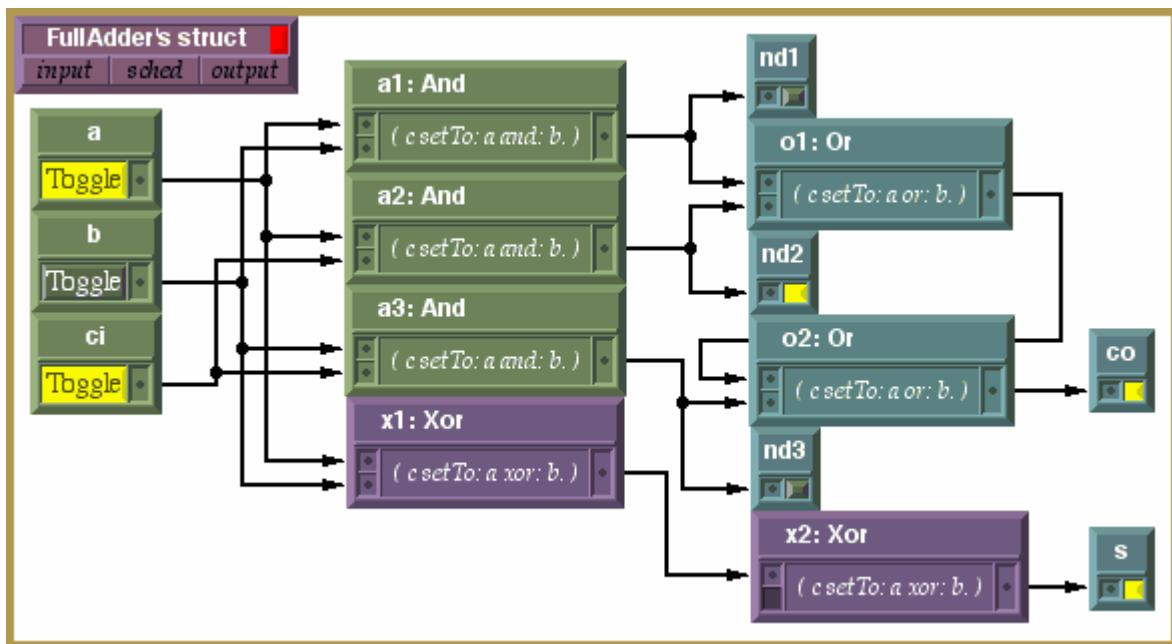

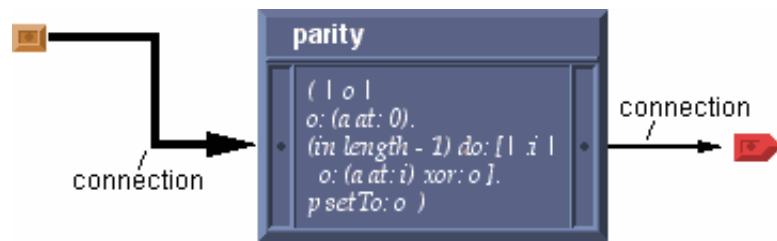

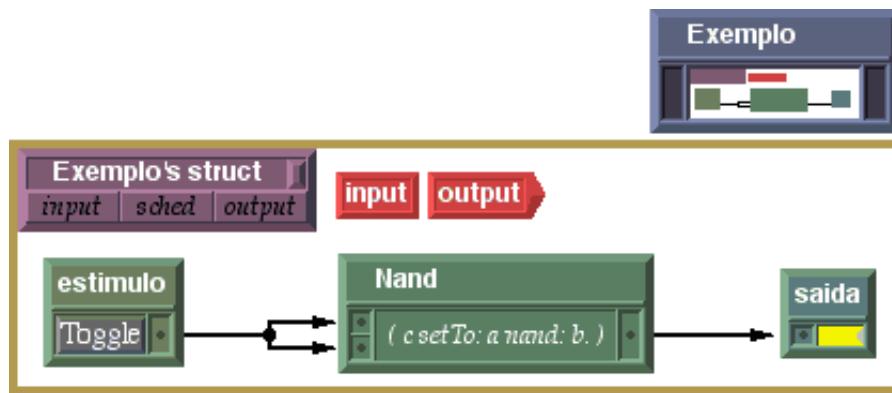

| 3.3  | Exemplo de uma descrição de <i>hardware</i> em que representações gráficas e textuais (SELFHDL) se misturam. . . . . | 85 |

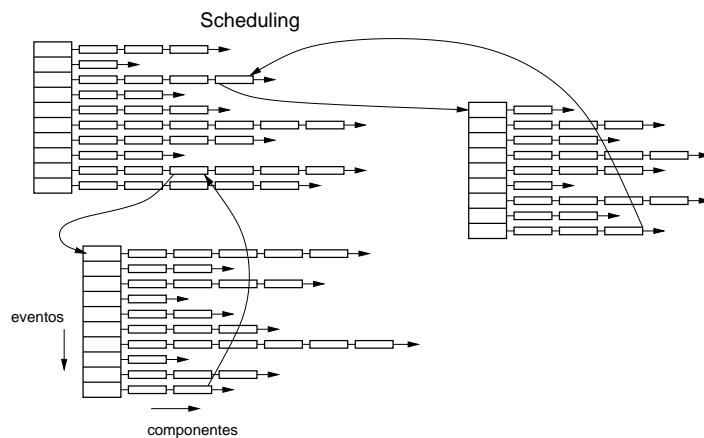

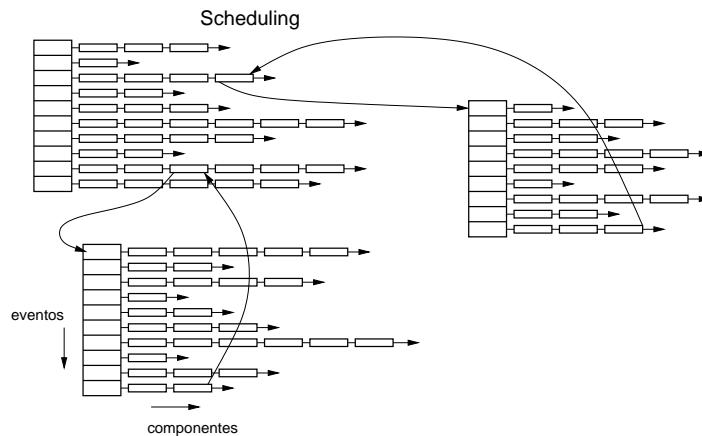

| 3.4  | Esquema de <i>scheduling</i> de avaliação de componentes. . . . .                                                    | 87 |

| 4.1  | Exemplo de uma descrição/Simulação SELFHDL. . . . .                                                                  | 92 |

|      |                                                                                                                                                                                                                                             |     |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

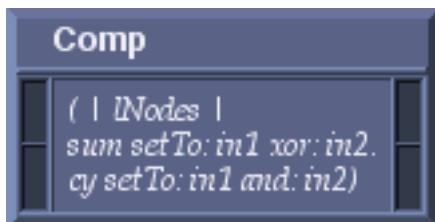

| 4.2  | Representação gráfica do objeto <code>comp</code> . . . . .                                                                                                                                                                                 | 94  |

| 4.3  | Esquema de avaliação da mensagem <code>behavior</code> num objeto <code>comp</code> . . . . .                                                                                                                                               | 96  |

| 4.4  | Representação gráfica de dois objetos <code>connection</code> . . . . .                                                                                                                                                                     | 99  |

| 4.5  | Listas de eventos e dependências de um objeto <code>schedulerMorph</code> . . . . .                                                                                                                                                         | 101 |

| 4.6  | Representação gráfica de um objeto <code>sComp</code> . . . . .                                                                                                                                                                             | 102 |

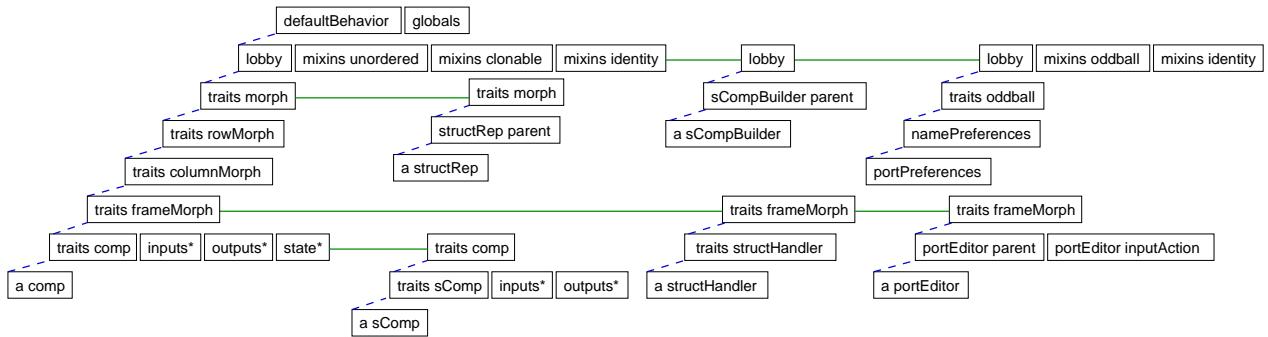

| 4.7  | Hierarquia dos objetos <code>comp</code> e <code>sComp</code> e alguns outros objetos auxiliares. . . . .                                                                                                                                   | 104 |

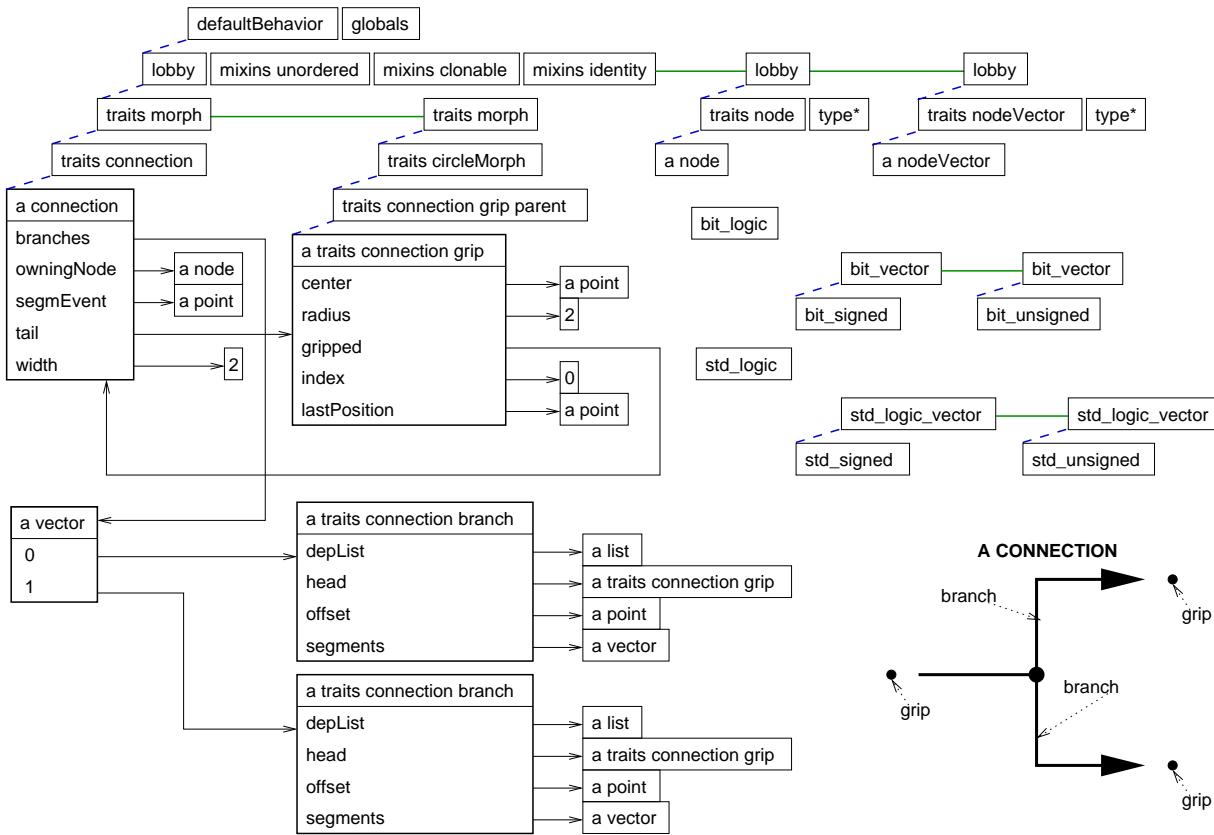

| 4.8  | Hierarquia dos objetos de conexão e tipos. . . . .                                                                                                                                                                                          | 106 |

| 4.9  | Hierarquia de outros objetos importantes. . . . .                                                                                                                                                                                           | 109 |

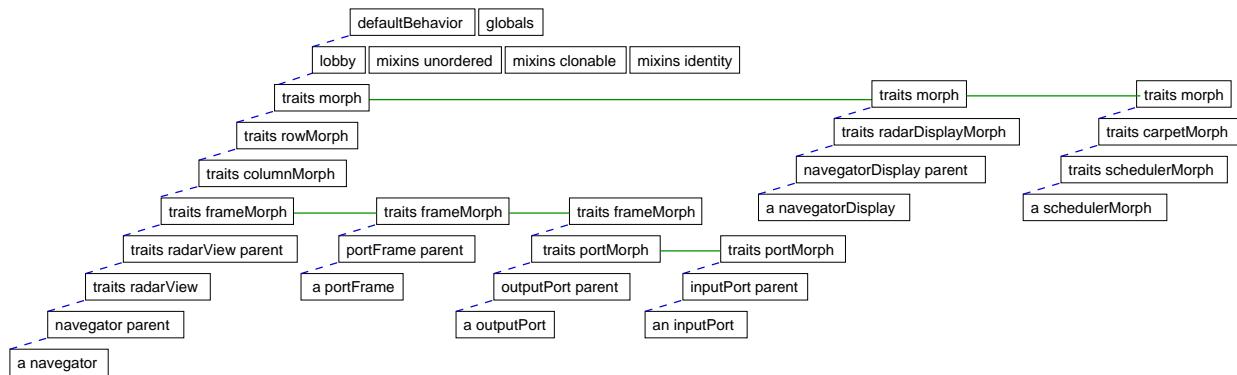

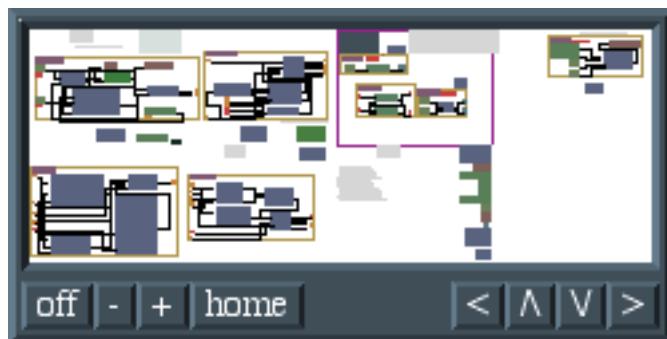

| 4.10 | Aparência gráfica de um objeto <code>navegator</code> . . . . .                                                                                                                                                                             | 111 |

| 4.11 | Hierarquia de objetos de inspeção e interação. . . . .                                                                                                                                                                                      | 111 |

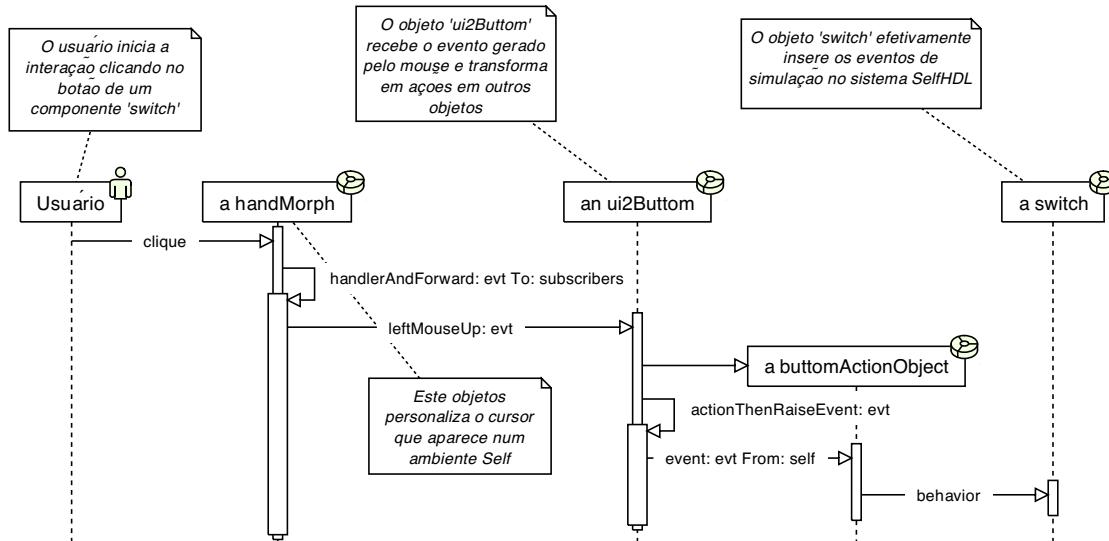

| 4.12 | Situação típica de simulação. . . . .                                                                                                                                                                                                       | 113 |

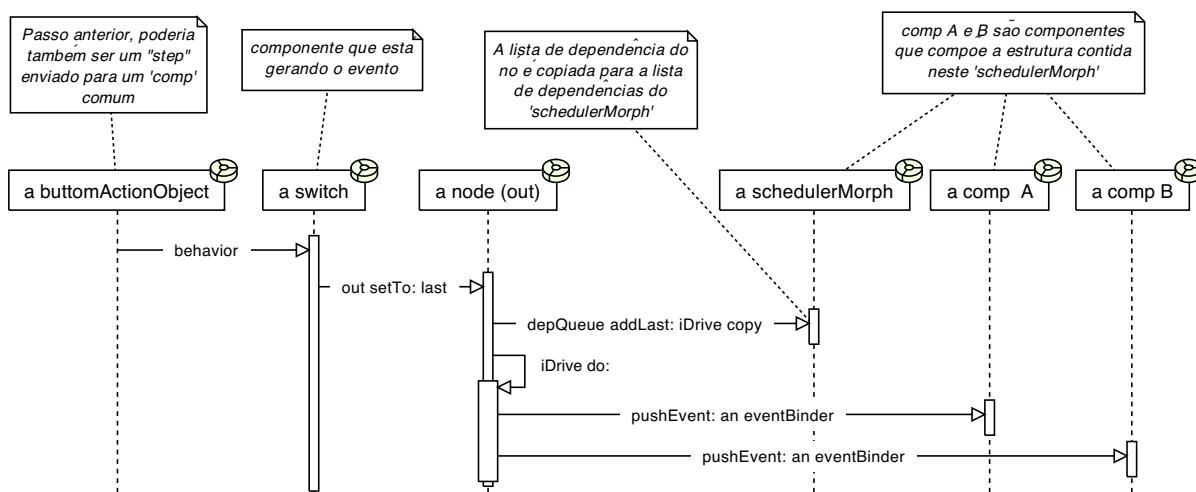

| 4.13 | Diagrama de seqüência para inserção de eventos externos, como interações com o usuário. . . . .                                                                                                                                             | 113 |

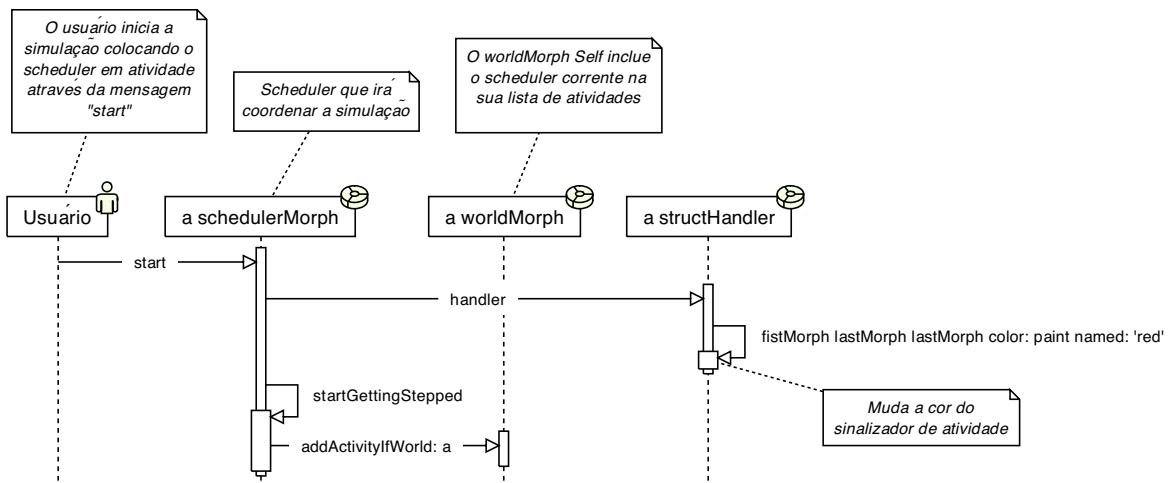

| 4.14 | Diagrama de seqüência para a propagação de eventos através dos objetos nós. .                                                                                                                                                               | 114 |

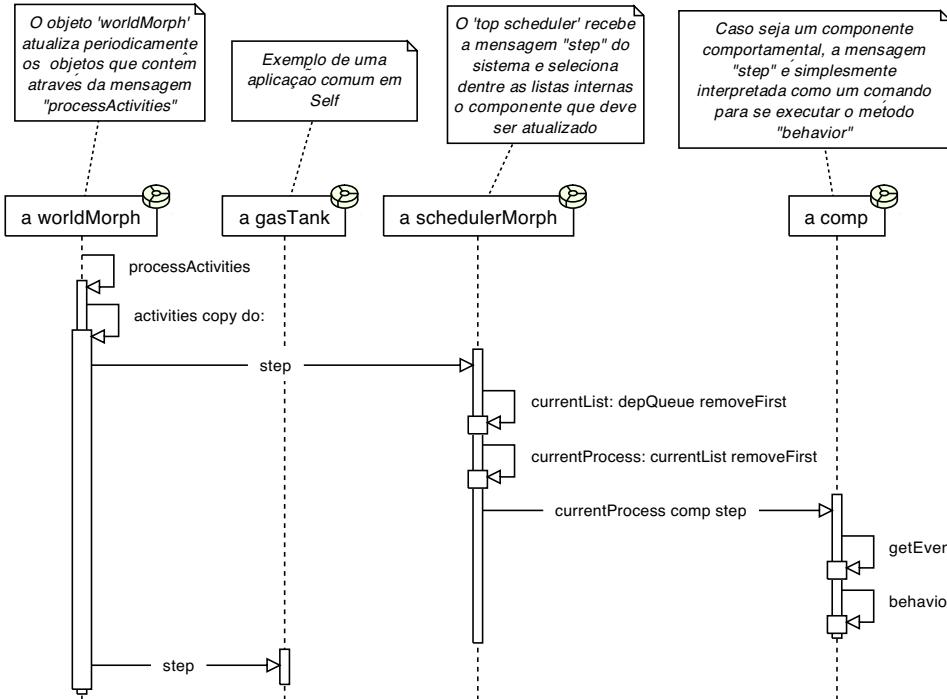

| 4.15 | Diagrama de seqüência para ativação de uma simulação. . . . .                                                                                                                                                                               | 115 |

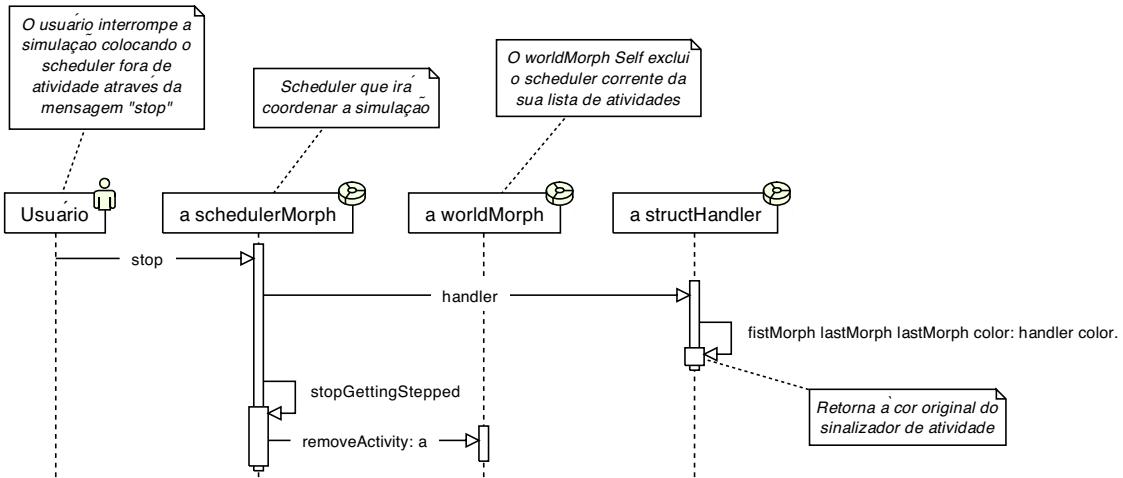

| 4.16 | Diagrama de seqüência para desativação de uma simulação. . . . .                                                                                                                                                                            | 116 |

| 4.17 | Diagrama de seqüência para avanço na simulação de um único nível. . . . .                                                                                                                                                                   | 116 |

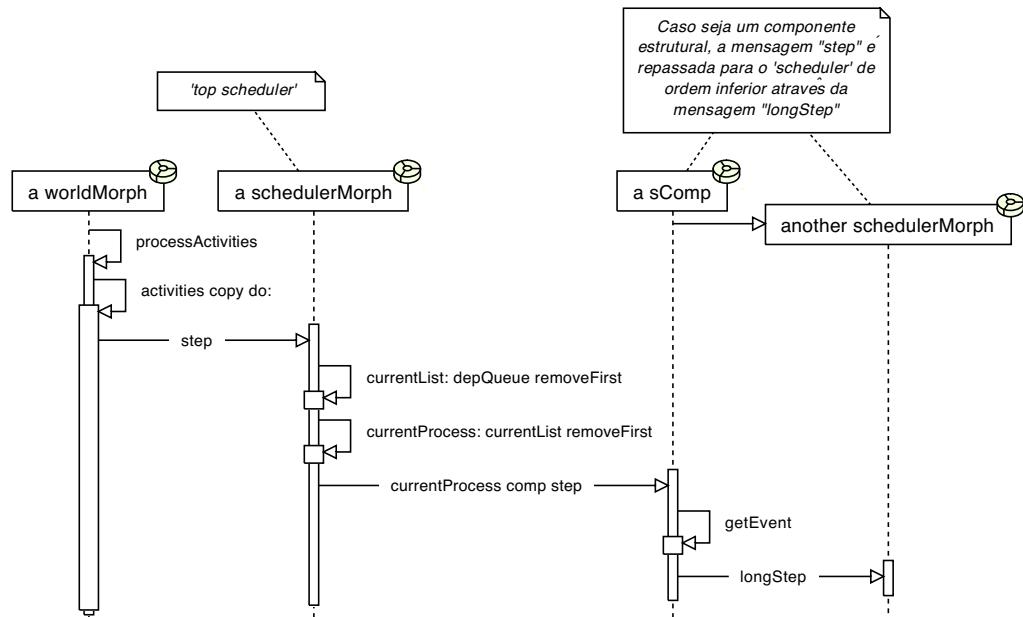

| 4.18 | Situação típica de uma simulação multi-nível. . . . .                                                                                                                                                                                       | 117 |

| 4.19 | Diagrama de seqüência para avanço na simulação multi-nível. . . . .                                                                                                                                                                         | 118 |

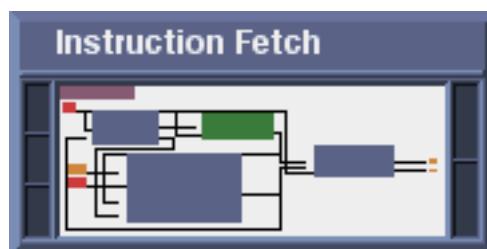

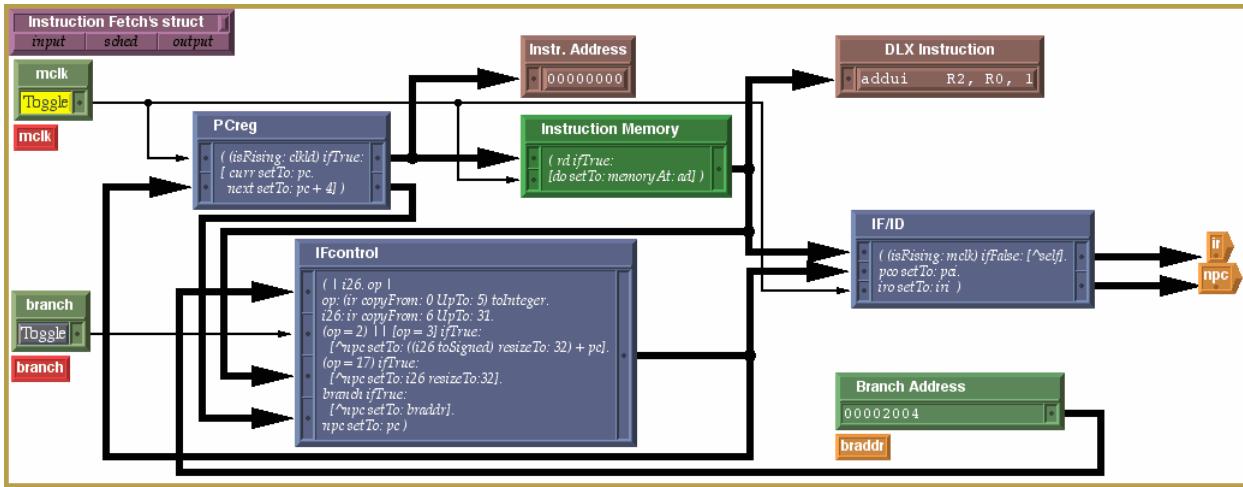

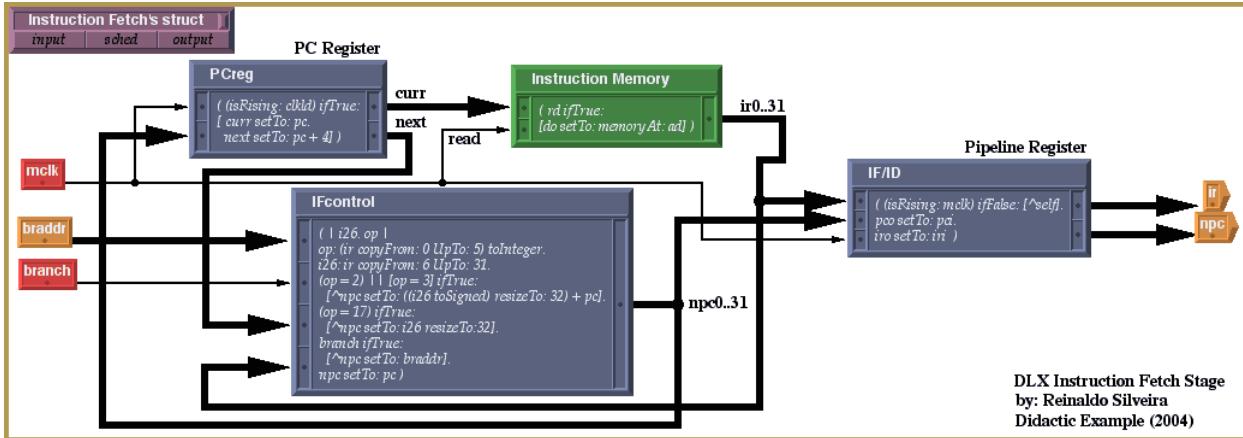

| 4.20 | Primeiro estágio de <i>pipeline</i> da arquitetura DLX. . . . .                                                                                                                                                                             | 120 |

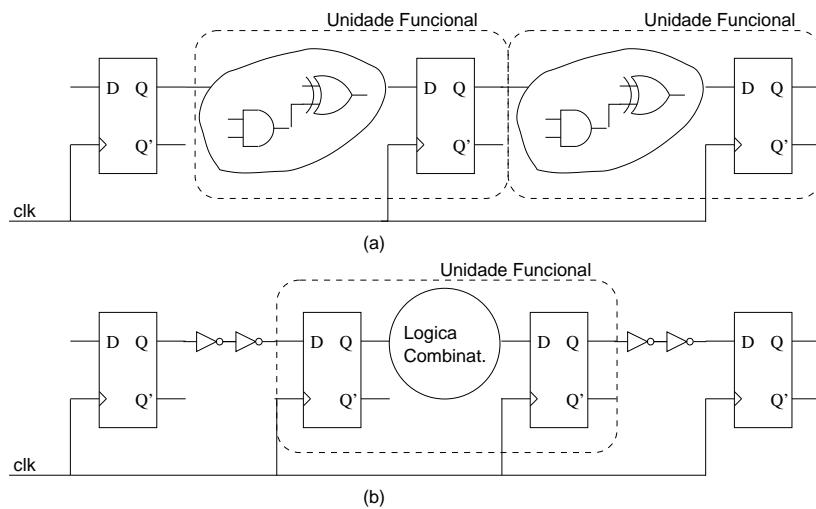

| 5.1  | Entradas e saídas registradas em unidades funcionais diferentes ajudam a controlar melhor a temporização do sistema: (a) Todas as entradas vindo de saídas registradas; (b) Registrando entradas e saídas na própria unidade funcional. . . | 125 |

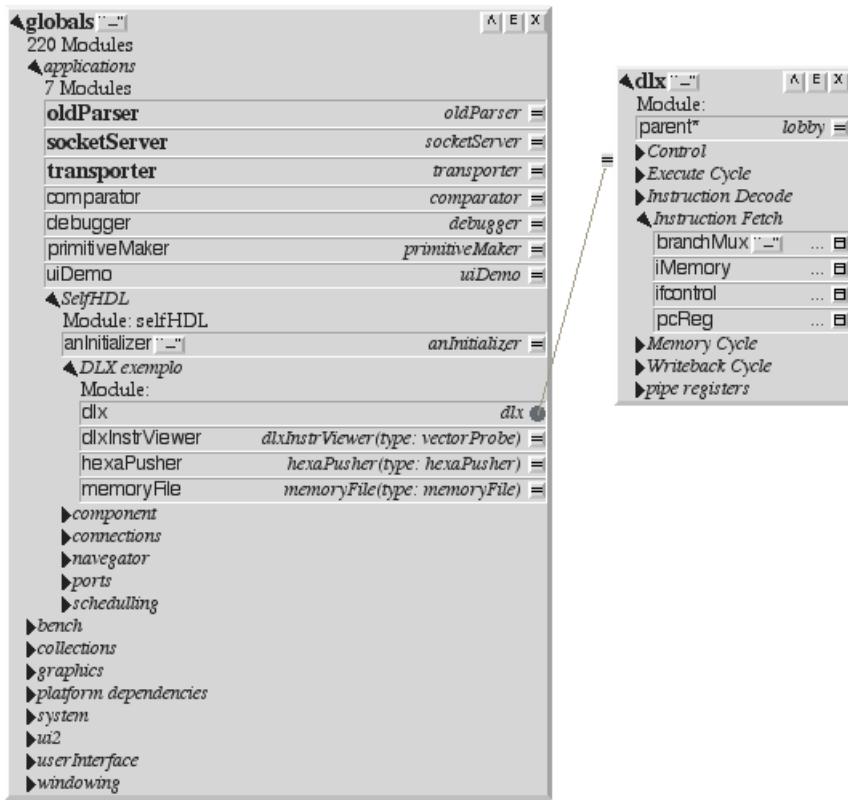

| 5.2  | Exemplo de um objeto repositório criado em <code>globals</code> . . . . .                                                                                                                                                                   | 129 |

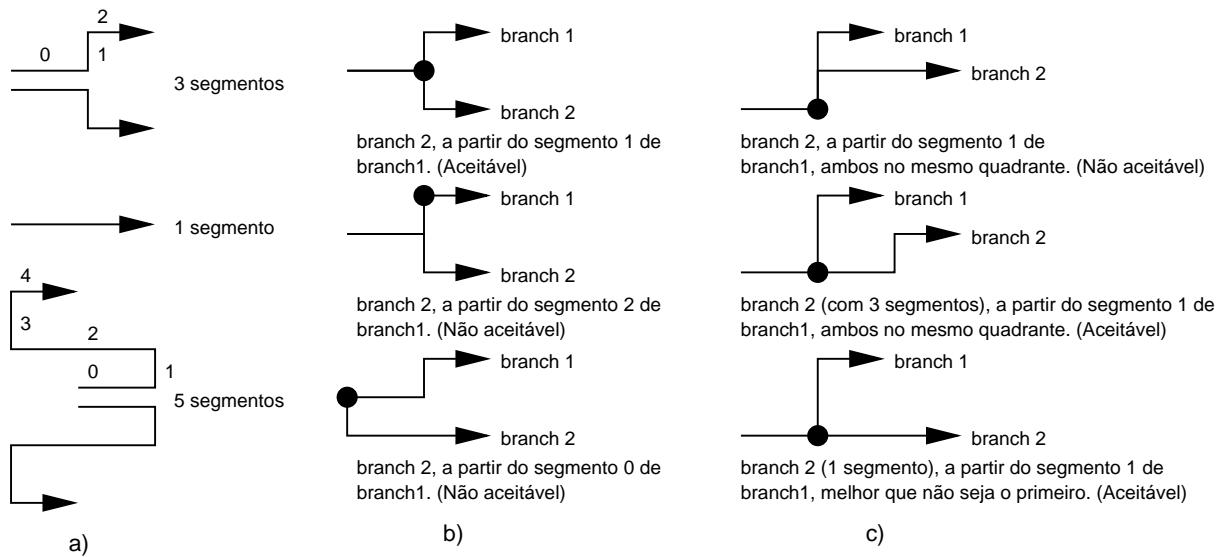

| 5.3  | a) Primeiro <i>branch</i> tem um número ímpar de segmentos. b) Segundo <i>branch</i> deve começar num ponto apropriado. c) Exemplos de múltiplos <i>branches</i> . . . . .                                                                  | 131 |

| 5.4  | Detalhe da figura 4.20 onde é mostrado os observadores de interesse. . . . .                                                                                                                                                                | 133 |

| 5.5  | Diagrama de seqüência de um estimulador não interativo. . . . .                                                                                                                                                                             | 135 |

| 5.6  | Diagrama de seqüência de uma simulação não interativa. . . . .                                                                                                                                                                              | 135 |

| 5.7  | Teste de um <code>memoryFile</code> . . . . .                                                                                                                                                                                               | 138 |

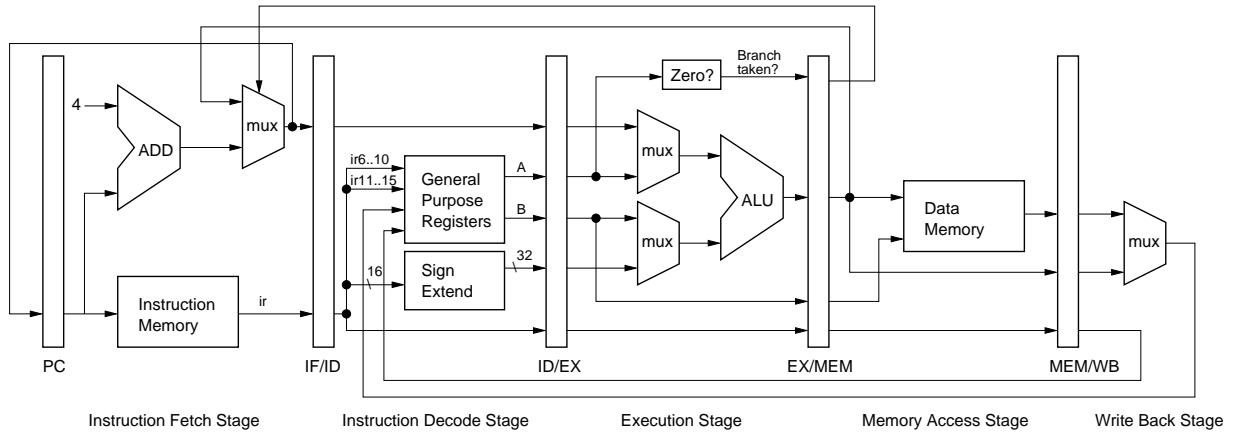

| 5.8  | Arquitetura <i>pipeline</i> do DLX. . . . .                                                                                                                                                                                                 | 141 |

---

|      |                                                                                                            |     |

|------|------------------------------------------------------------------------------------------------------------|-----|

| 5.9  | Exemplo de uma seqüência ideal de instruções no <i>pipeline</i> do DLX. . . . .                            | 143 |

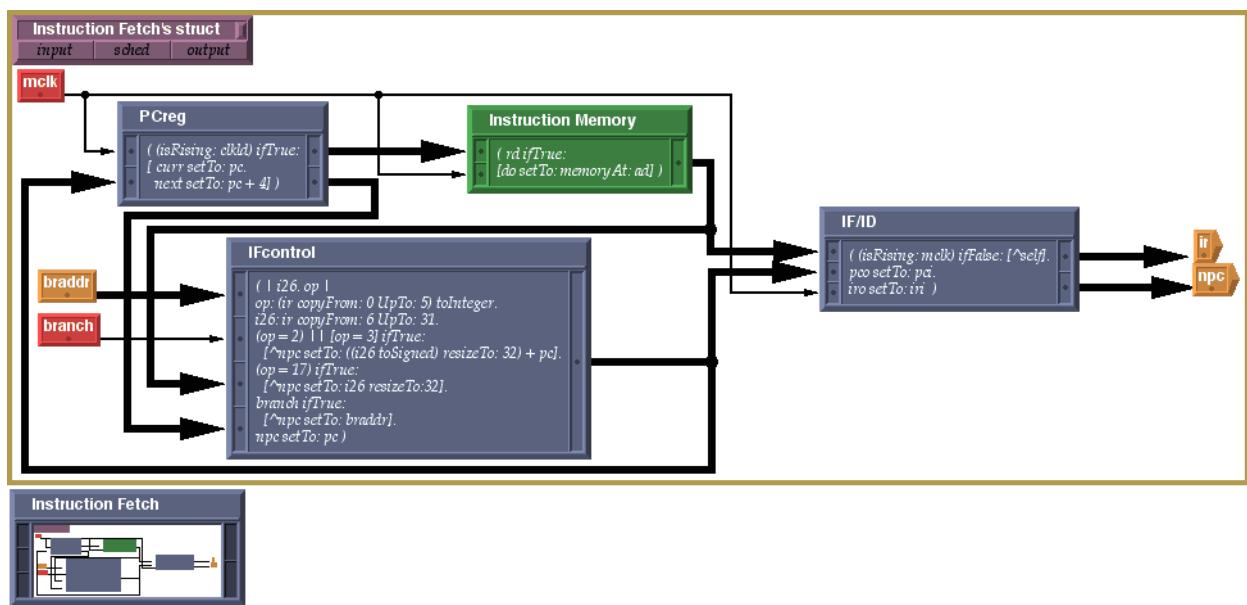

| 5.10 | Estágio de busca de instruções no <i>pipeline</i> do DLX. . . . .                                          | 143 |

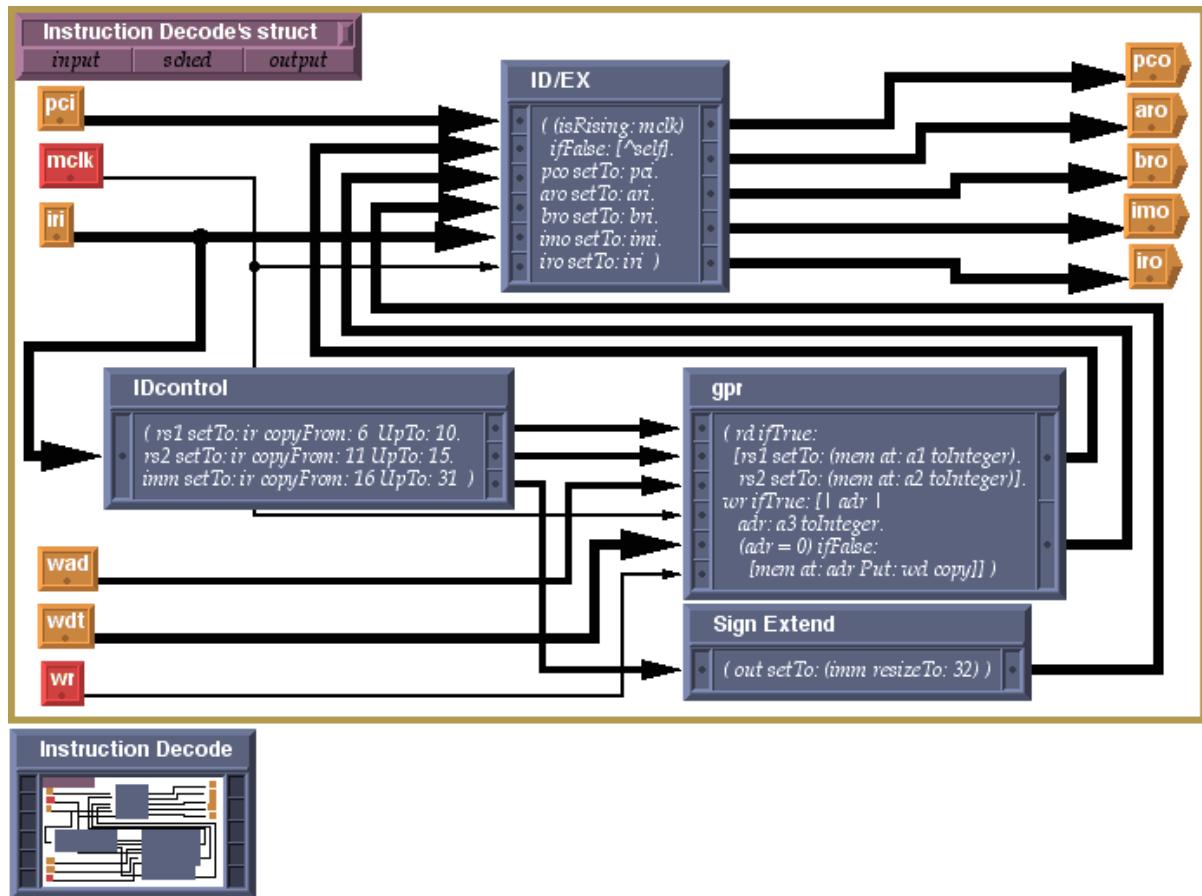

| 5.11 | Estágio de decodificação e busca de operandos no bando de registradores no <i>pipeline</i> do DLX. . . . . | 145 |

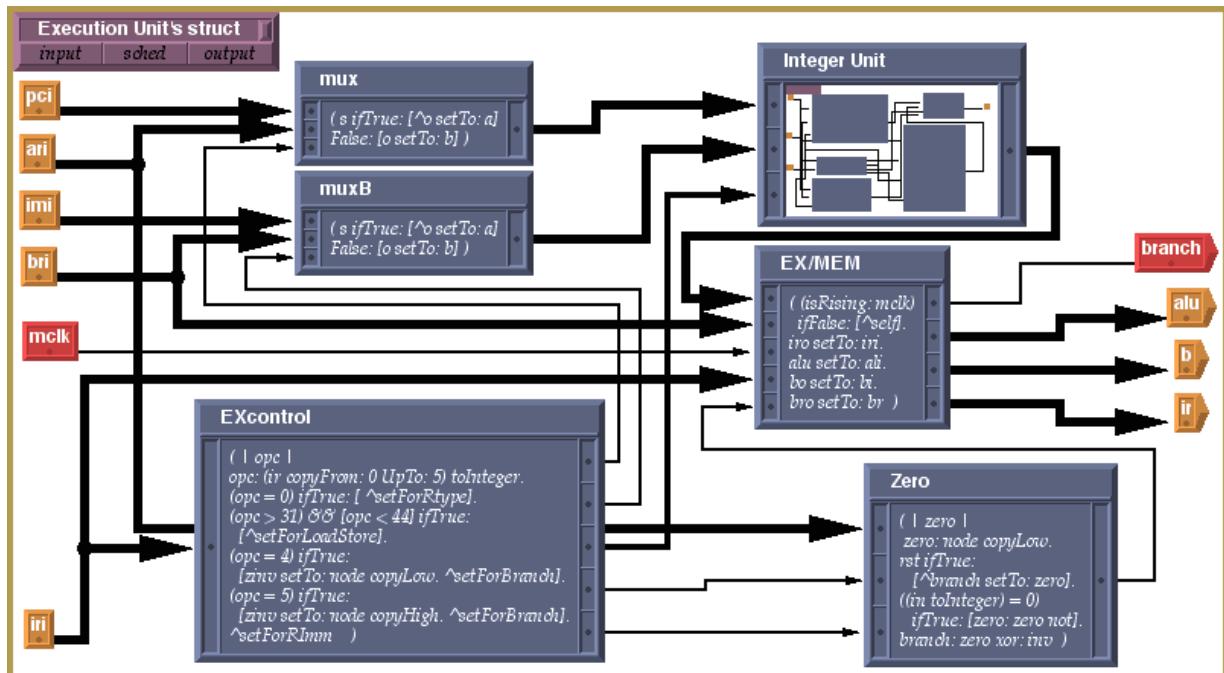

| 5.12 | Estágio de execução ou cálculo de endereço no <i>pipeline</i> do DLX. . . . .                              | 147 |

| 5.13 | Detalhe da Unidade de Execução com Inteiros do DLX. . . . .                                                | 148 |

| 5.14 | Estágio de acesso a memória do <i>pipeline</i> do DLX. . . . .                                             | 149 |

| 5.15 | Estágio de <i>Writeback</i> do <i>pipeline</i> do DLX. . . . .                                             | 150 |

| 5.16 | Implementação da arquitetura <i>pipeline</i> do DLX. . . . .                                               | 152 |

| 6.1  | Exemplo do uso de <i>labels</i> numa descrição SELFHDL. . . . .                                            | 156 |

| A.1  | Formato de Instruções do DLX. . . . .                                                                      | 164 |

# **Lista de Tabelas**

|                                                                               |     |

|-------------------------------------------------------------------------------|-----|

| 2.1 Avaliação de algumas linguagens de descrição de <i>hardware</i> . . . . . | 42  |

| A.1 Instruções DLX de acordo com campo “ <i>Opcode</i> ” . . . . .            | 162 |

| A.2 Instruções DLX de acordo com o campo “Função Especial” . . . . .          | 163 |

# Capítulo 1

## INTRODUÇÃO

**N**O início da microeletrônica, a complexidade era relativamente baixa, o correto dimensionamento dos componentes eletrônicos era o fator crítico do projeto. Durante muito tempo, essa foi a característica dos projetos, arquiteturas relativamente simples implementadas em tecnologias constantemente em mutação (TTL, NMOS, CMOS, BiCMOS, etc.). Era natural que as metodologias e ferramentas acompanhassem esse desenvolvimento. O custo de implementação dos circuitos integrados era relativamente elevado e custoso em tempo que a margem de erro admissível em um projeto era praticamente zero\*. Desse modo, foi elaborado um vasto conjunto de ferramentas de verificação e simulação de forma a diminuir as possibilidades de erro lógico/estrutural, e assim a viabilizar a implementação de um novo circuito integrado.

Atualmente, a complexidade de alguns sistemas alcança a ordem de dezenas de milhões de componentes numa única pastilha de silício (*Systems on a Chip*) e ainda são utilizadas metodologias e ferramentas concebidas há mais de vinte anos. Obviamente essas ferramentas também evoluíram, mas continuam atuando na parte de implementação do componente. Houve uma grande evolução nos algoritmos, nas estruturas de dados e na automatização, tornando a tarefa de implementação quase que automática em alguns casos. A concepção de novas arquiteturas, no entanto, ainda continua sendo um trabalho quase que puramente intelectual.

Hoje em dia, a maior parte do tempo de desenvolvimento é gasto na concepção do sistema

---

\*Hoje, nas tecnologias mais sofisticadas, esses custos são tão altos que os erros precisam ser totalmente erradicados.

e na definição funcional/arquitetural/estrutural, enquanto que a implementação em si passa a ocupar apenas um quinto do tempo total de projeto. No passado, essa razão era inversa, daí o tremendo desenvolvimento experimentado pelas ferramentas nas últimas décadas. O momento é de rever a forma com que são pensadas as ferramentas de projeto, atacando o problema da concepção de sistemas. Portanto, o intuito deste trabalho é traçar as diretrizes básicas de uma nova metodologia de projetos digitais que suplante as dificuldades de projeto de sistemas digitais extremamente complexos e que seja o ponto inicial do desenvolvimento de um novo conjunto de ferramentas que darão suporte a essa nova metodologia.

No início da década de 80, houve uma grande dificuldade de adaptação dos projetistas de circuitos integrados ao novo cenário que então se configurava. Devido ao rápido desenvolvimento das tecnologias VLSI, a pressão por dispositivos mais complexos, num nível de integração mais elevado, tornava a tarefa de projeto árdua, demorada e custosa. O custo de implementação dos protótipos também fazia com que fosse necessário elevar o grau de confiabilidade dos elementos projetados. Isso levou o Prof. Daniel D. Gajski [Gaj88] a chamar esse período de “*design crisis*” dos anos 80.

Duas estratégias foram adotadas para superar as dificuldades. Uma levava em consideração que o homem era a principal fonte de conhecimento, portanto a automação deveria prover ferramentas que aumentassem a sua produtividade. A segunda considerava que o conhecimento necessário para fazer projeto poderia ser “capturado” e encerrado em programas, os chamados “*Silicon Compilers*”, que por sua vez poderiam gerar os dispositivos VLSI automaticamente, a partir de uma descrição de “alto nível”. De fato essas duas estratégias deram um grande impulso aos projetos de sistemas VLSI pois permitiram aos projetistas alcançar um nível de abstração em que detalhes de implementação e fabricação não eram mais necessários.

O termo “*Silicon Compilation*” foi apresentado pela primeira vez por Dave Johannsen [Gaj88], quando se referia ao conceito de montagem parametrizada de peças de *Layout*. O termo tornou-se muito popular e rapidamente assumiu uma conotação muito mais ampla do que a originalmente proposta. Na realidade, a compilação de silício é uma extensão do conceito de *Standard-cell*, em que células padronizadas são posicionadas e interligadas junto com células especiais geradas por *cell compilers*. Mais recentemente a geração de componentes complexos apresentando microarquitetura regular e/ou simétrica, como ROMs,

RAMs, PLAs, ALUs, etc, tem sido associada às funções dessa classe de programas. De forma geral, parece mais conveniente entender o termo pelo seu aspecto mais amplo, ou seja, devemos entender a compilação de silício apenas como o processo de obtenção do *layout* a partir de uma descrição de alto nível.

Um outro conceito, seguindo a estratégia dos compiladores de silício, de aumentar a inteligência dos programas, é o da síntese de alto nível. Nele, uma arquitetura poderia ser sintetizada a partir de uma descrição de alto nível, possivelmente algorítmica. Nessa área existem alguns avanços; entretanto, pelo fato de ser muito difícil se definir objetivamente o que é realmente alto nível e também se mapear todas as classes de problemas/soluções, as ferramentas existentes acabaram suportando apenas alguns problemas específicos (muito devido a sua regularidade, como por exemplo o processamento digital de sinal), proliferando-se especialmente nos meios acadêmicos.

Analizando mais profundamente as duas estratégias, podemos notar que seu propósito inicial era atacar o problema de projeto em dois níveis diferentes: o da concepção, no caso dos compiladores de silício e síntese de alto nível; e o da implementação, no caso das demais ferramentas de CAD. Infelizmente, tanto a compilação quanto a síntese de alto nível, alcançaram mais sucesso em termos de implementação do que de concepção propriamente dita, mais uma vez, em função de inconsistências do que seria realmente alto nível ou não.

## 1.1 Justificativa e Motivações

O processo de criação de uma arquitetura (concepção de uma solução de *hardware*) passa por várias fases: Definição/Análise do Problema; Projeto do Sistema; Projeto dos elementos componentes; e finalmente Implementação. Obviamente, dada a alta complexidade dos problemas que existem atualmente, ferramentas computacionais são necessárias em cada uma das suas etapas. O objetivo final é a obtenção de uma descrição que possa ser compartilhada com as fases posteriores de implementação. No caso de um sistema digital, essa descrição é tipicamente uma descrição feita utilizando uma linguagem de descrição de *hardware* em nível RTL (*Register Transfer Level*). A partir de tal descrição, poderiam ser usadas ferramentas tradicionais de síntese lógica e compilação de silício para implementar o protótipo.

Dependendo do grau de estruturação do projetista, podemos identificar as mesmas eta-

pas de desenvolvimento de um sistema de *software* orientado a objeto, talvez em função da própria natureza das ferramentas utilizadas. A verdade é que a grande maioria das ferramentas foi desenvolvida por cientistas de computação e não por engenheiros de projeto digital/eletrônico. A visão predominante dessas ferramentas é impregnada com o perfil dos profissionais de computação e não com os de engenharia, o resultado é que o fluxo de projeto e as tarefas em geral não seguem um padrão muito intuitivo para o profissional técnico.

Tomemos um exemplo simples: Ao desenvolver um projeto temos como objetivo a obtenção de uma descrição de sistema numa linguagem de descrição de *hardware*, por exemplo VHDL, em nível RTL (sintetizável). Na etapa de definição/análise do problema é comum a necessidade de serem feitas experimentações a fim de se entender melhor o problema que se quer resolver; para tal, as linguagens de descrição de *hardware* oferecem uma modalidade chamada de “comportamental” para descrever os módulos de *hardware* não exatamente como eles devem ser implementados, mas apenas, como espera-se que seja o seu comportamento externo. Isso é feito pois o comportamento é em geral mais fácil de ser descrito do que a real estrutura interna. Dá-se o nome a isso de “Níveis de Abstração”, ou seja, abstrair a estrutura e focalizar somente a função. Infelizmente, as linguagens dedicadas a descrição de *hardware* são muito limitadas em alguns aspectos, sendo muito comum o projetista ter que optar por usar uma outra linguagem mais flexível para obter resultados mais rapidamente. O engenheiro é obrigado assumir o papel de programador para completar a tarefa.

Nas Etapas seguintes, Projeto do Sistema e dos Elementos componentes, segue mais ou menos os mesmos passos em termos de ferramentas. A descrição comportamental em uma HDL (*Hardware Description Language*) qualquer ou numa linguagem de uso geral como C ou C++, e mais todo o *overhead* associado, *makefiles*, listagens, *includes*, bibliotecas de funções, compilações, simulações, análise de resultados, correções e mais um novo ciclo de iterações se inicia. Ou seja, é um típico projeto de software usando ferramentas para desenvolvimento de software para se fazer um projeto de *hardware*.

A Etapa final: a de Implementação seria a mais ligada à implementação propriamente dita (e ao objetivo desse tipo de desenvolvimento). A descrição RTL tem mais semelhança com a estrutura física do componente do que seu comportamento. Por seguir regras rígidas, a descrição RTL muitas vezes é incompatível com as descrições até então obtidas nas etapas anteriores, sendo muitas vezes necessário que as mesmas sejam rescritas para que essa

conformidade seja alcançada. Mesmo nessa etapa são utilizadas as mesmas ferramentas e técnicas anteriores, ou seja, tipicamente metodologias de desenvolvimento de software.

Podemos destacar várias desvantagens nesse tipo de abordagem. O mais imediato é da necessidade de transformarmos um profissional de engenharia num profissional de computação. Apesar dos cursos de engenharia possuírem uma boa carga de programação, ainda é necessário um bom treinamento do profissional a fim de capacitá-lo para esse tipo de tarefa. Para um projeto deste tipo, não basta que o profissional tenha um bom raciocínio algorítmico, mas também é necessário que o mesmo possa raciocinar em termos de componentes e portas lógicas.

Outra desvantagem, diz respeito ao ciclo de projeto de software. O ciclo: edição, compilação, simulação e análise, é intrinsecamente desconexo; foi concebido para trabalhar em *batch* ou *background* numa época em que o tempo de processamento era caro e eram utilizados *Mainframes*. Acreditamos que um desenvolvimento deve ser interativo, contínuo, ininterrupto a fim de evitar que o projetista se disperse em pensamentos não relacionados a tarefa em processo. Segundo a metodologia corrente, podem transcorrer vários minutos entre uma correção e a análise de um detalhe em particular, tempo esse em que o projetista tem que iniciar uma outra tarefa ou tomar um “cafezinho” para aproveitar o tempo ocioso, dispersando-se invariavelmente dos detalhes importantes do projeto.

## 1.2 Objetivos

Este trabalho propõe uma forma alternativa de se fazer o projeto digital, chamada “Metodologia Orientada ao Projetista”, ou simplesmente DO (*Designer Oriented Methodology*). Essa metodologia procura enfatizar alguns princípios fundamentais, como:

- O processo de criação precisa ser interativo.

- O nível de abstração que se deseja alcançar é o RTL, para que as etapas posteriores de implementação permaneçam inalteradas.

- O nível de abstração usada nas fases intermediárias deve ser indeterminada, tão grande quanto se queira (ou que seja necessária).

- Os elementos de *hardware* apresentam características autônomas, ou seja, incorporam automaticamente o comportamento atribuído sem a necessidade de grandes intervenções do projetista.

- Assim como os ambientes gráficos apresentam a metáfora da mesa de trabalho (*Desktop Metaphore*) nos computadores atuais, a nova metodologia deve apresentar a metáfora da bancada de trabalho.

- Utilização de ferramentas computacionais para dar suporte aos itens anteriores. Neste trabalho é implementado o sistema SELFHDL para descrição de *hardware* digital, indicado especialmente para a concepção e exploração de arquitetura de sistemas digitais.

A fim de possibilitar a concretização dessa metodologia, um grande suporte computacional foi necessário. A utilização de uma linguagem de programação de alto nível, orientada a objetos, com características de interatividade e acessibilidade aos objetos tem sido de muita ajuda na implementação desse suporte computacional. Escolhemos então, a linguagem SELF [US87] para cumprir essa função. SELF é uma linguagem de programação orientada a objeto baseada em protótipos e tipos dinâmicos desenvolvida em 1986 por David Ungar e Randall B. Smith no Xerox PARC. Concebido como uma alternativa a linguagem Smalltalk-80 [GR83], SELF procura maximizar a produtividade através de um ambiente de programação exploratório, ao mesmo tempo mantendo a linguagem simples e pura sem com isso comprometer a expressividade a maleabilidade.

### 1.3 Convenções

Neste trabalho optamos por não traduzir os termos técnicos comumente usados na área de projeto de sistemas digitais e ferramentas de CAD, com exceção dos casos nos quais algum esclarecimento se faça necessário. Portanto, todas as palavras de línguas estrangeiras são apresentados em caracteres *itálicos*, por exemplo: *bits*, *bytes*, *Hardware Description Language*. No decorrer da apresentação faremos referência também a elementos de *software*, como listagens de programas, objetos, etc. Neste caso utilizamos caracteres de espaçamento constante e tipo “courier”. Neste caso ainda, se faz necessária a distinção entre mensagem e objeto, muito peculiar quando descrevemos elementos do SELF ou do SELFHDL. Portanto,

convencionamos nos referir a mensagens colocando-as entre aspas (""), além do tipo "courier", quando elas aparecem no meio do texto explicativo. Por exemplo: o objeto `circleMorph` possui o método "position" que retorna a posição do centro do circulo em coordenadas cartesianas. A mensagem "color: aColor" modifica a cor do objeto para o novo valor `aColor`. Outras ocasiões podemos usar as aspas simplesmente para chamar a atenção para o termo, como nesta frase ou quando falamos do tipo "courier" nesta seção. Outro exemplo do uso de aspas pode ser visto na seção 2.2.5.1, quando nos referimos ao nome de alguns objetos. O nome de alguns objetos pode ser composto por mais de uma palavra, portanto, para maior clareza, utilizamos as aspas para destacá-lo do texto que o circunda, por exemplo: "a point" é o nome de um objeto do tipo `point`.

## 1.4 Organização da Tese

No capítulo 2 apresentamos um levantamento das principais ferramentas atualmente em desenvolvimento na área de projeto de sistemas digitais e circuitos integrados. Situamos cada desenvolvimento, comparativamente em relação a este trabalho. Neste capítulo apresentamos ainda os fundamentos da linguagem SELF, a fim de realçar as qualidades que a tornaram elegível para a realização deste trabalho e prover um embasamento para seja possível o entendimento da implementação do SELFHDL. Este capítulo não deve ser encarado como uma espécie de tutorial, mais sim uma referência para aqueles que não estão familiarizados com as filosofias usadas por uma certa classe de linguagens orientadas a objeto, da qual faz parte a linguagem SELF.

No capítulo 3 apresentaremos a metodologia de projeto orientada ao projetista (DO), além de alguns dos motivos que nos levaram a proposição desta metodologia alternativa. Fazemos um desenvolvimento e argumentação teórica/filosófica baseados em certos princípios de hermenêutica, e iniciaremos a descrição detalhada das características desejadas em ferramentas dessa metodologia. Finalmente, concluímos o capítulo discutindo superficialmente as características potenciais do sistema SELFHDL, utilizado neste trabalho para demonstrar a metodologia DO.

No capítulo 4 apresentamos a implementação do sistema SELFHDL, no qual mostramos um detalhamento da implementação dos objetos principais e respectivas dinâmicas, bem

como a apresentação dos primeiros exemplos.

No capítulo 5 apresentamos os testes realizados, utilizando o sistema SELFHDL. Mostramos como as descrições SELFHDL são superiores em relação às descrições VHDL, através da implementação da arquitetura do processador DLX. Essa implementação é comparada a duas outras implementações clássicas e veremos como o nível de expressividade das formas tradicionais é inferior em relação à nossa proposta. Vemos também que os recursos de simulação interativa do sistema SELFHDL o tornam um ambiente propício à experimentação de arquiteturas e como ferramenta de apoio didático.

Finalmente no capítulo 6 apresentamos um resumo das conclusões gerais deste trabalho e possibilidades e motivações futuras em relação à metodologia e ao sistema SELFHDL, a fim de torná-lo mais poderoso e flexível.

# Capítulo 2

## ESTADO DA ARTE

NESTE capítulo, faremos uma apresentação do cenário de desenvolvimento de ferramentas de CAD para projeto digital em geral. O nosso intuito é situar o trabalho dentro dos vários campos de pesquisa existentes nos últimos anos, bem como servir como base para os conceitos que introduziremos.

A abordagem sobre ferramentas terá em princípio um caráter apenas de demonstração, evitaremos sempre que possível entrar em detalhes técnicos ou muito complicados, que não são o objetivo deste trabalho. Por outro lado, faremos também a apresentação da linguagem de programação SELF que será utilizada por nós e que é responsável por muitos dos conceitos que introduziremos. A apresentação da linguagem SELF se faz necessária, pois diferente de outras linguagens, SELF é muito diferente em vários aspectos. Sendo em geral pouco familiar a grande parcela dos programadores.

### 2.1 Estado da Arte em Ferramentas de Projeto Digital

Desde o surgimento dos primeiros dispositivos integrados na década de 60 até os dias de hoje, o projeto de circuitos integrados tem sido um grande desafio. Alguns aspectos deste desafio foram se modificando ao longo dos anos; porém, todos os esforços parecem obedecer ao que veio a ser conhecida como “Lei de Moore” [Cor04], enunciada por Gordon E. Moore (fundador da Corporação Intel) em 1965 [Moo65]. Neste artigo, Moore prevê a importância dos dispositivos integrados e observa que até então a taxa de integração vinha sendo dobrada a cada dois anos.

A indústria de circuitos integrados, de modo geral, tomou esse enunciado como postulado, direcionando todos os seus esforços no sentido de manter essa premissa verdadeira. Por outro lado, tem-se criado também uma expectativa, no mesmo sentido, por parte dos consumidores, que pressionam a demanda por produtos com as mesmas taxas de aperfeiçoamento ditadas por essa lei. A Intel, por exemplo, é uma das empresas que se orgulham em mostrar a evolução da sua linha principal de produtos de acordo com a lei de Moore [Moo03], veja por exemplo a figura 2.1.

Figura 2.1: Lei de Moore de acordo com a linha de processadores Intel.

Desde então, a tecnologia tem evoluído segundo esses padrões e às custas de grandes investimentos, fazendo com que, ainda hoje, o projeto e a fabricação de circuitos/sistemas integrados esteja fora do alcance da grande maioria das pessoas. Filosofias a parte, por muitos anos o custo tecnológico esteve concentrado nos processos de fabricação dos circuitos. A instabilidade dos processos e os baixos rendimentos faziam com que o custo dos dispositivos ficassem muito elevados. Nessa época, começaram a surgir as ferramentas de auxílio ao projeto eletrônico. Apesar dos circuitos serem bem conhecidos, o tamanho dos mesmos e a funcionalidade crescente demandava incontáveis horas de verificação, pois um CI que não funcionasse após a fabricação era caro demais para ser tolerado. A técnica de *breadbording*

era aplicada sempre que possível durante o desenvolvimento, porém, não era garantia de sucesso. A passagem do circuito conceitual para o micro circuito era feito invariavelmente sob intervenção humana, resultando num grande número de erros potenciais.

Surgiram, então, os primeiros simuladores e sistemas de verificação de *layout*. Em seguida, programas de captura esquemática, pois até então circuitos elétricos e eletrônicos eram invariavelmente representados em termos de diagramas esquemáticos. Esse método de captura-simulação deu muito certo e tem sido popular por mais de três décadas [Gaj93]. Outros aperfeiçoamentos importantes foram introduzidos como o conceito de níveis hierárquicos e células básicas que poderiam e seriam utilizadas por todo o projeto, estruturas regulares como memórias e PLAs, e etc [MC80, WE88].

Todos esses aperfeiçoamentos junto com a consolidação dos processos de fabricação fizeram com que a pressão por circuitos mais complexos aumentasse, e com ela as dificuldades, o tempo e os custos dos projetos. O Prof. Gajski chamou este período de “*Design Crisis*” dos anos 80 [Gaj88, DG90]. Estava claro naquela época que ferramentas\* que aumentassem a produtividade dos projetistas não eram suficientes para lidar com as demandas que estavam surgindo. Essas ferramentas seguem uma linha de pensamento que diz que o processo de desenvolvimento de um circuito integrado é muito difícil de ser concebido por meios automáticos, e que o projetista humano é a principal fonte de conhecimento para esse fim. Portanto, as ferramentas devem promover a produtividade do projetista humano através da automatização de tarefas rotineiras e/ou aumento de eficiência em outras. São em geral ferramentas de captura, verificação, análise e otimização. Por exemplo: simuladores, verificadores de regras *layout*, analisador de temporização (*timing*), compactadores e etc. São ferramentas que automatizam tarefas repetitivas, longas e cansativas.

Nessa época surgiu a idéia de que era possível a criação de ferramentas de síntese e compilação capazes de gerar o *layout* de sistemas VLSI automaticamente. Essas ferramentas gerariam o *layout* a partir de alguma descrição de “alto nível” do sistema, que poderia ser um *layout* simbólico, um diagrama esquemático de um circuito, uma descrição comportamental de uma microarquitetura, conjunto de instruções ou um algoritmo de processamento de sinais. Essas ferramentas ficaram conhecidas genericamente como “Compiladores de Silício”.

---

\*Usaremos normalmente o termo ferramenta no sentido de ferramenta computacional, ou seja, programas desenvolvidos especificamente para determinadas tarefas.

As duas estratégias tiveram bons resultados. A experiência nos tem mostrado que as duas abordagens quando usadas conjuntamente podem produzir ferramentas muito eficientes para a implementação dos circuitos. Entretanto, ao longo de toda a história, essas ferramentas se ocuparam exclusivamente com a implementação dos circuitos em silício, pois até então a fabricação era o fator mais custoso e determinante do sucesso de um projeto.

No final dos anos 80 e início dos 90, outros aspectos tornaram-se mais importantes na implementação de sistemas VLSI. Os processos de fabricação ficaram mais ou menos equivalentes, diversos fabricantes ofereciam tecnologias que seguiam tendências bem estabelecidas e que implementavam circuitos com desempenho semelhante; assim a única forma de diferenciar seus produtos e torná-los mais competitivos era empregar melhorias nas técnicas de circuito e no emprego de novas arquiteturas. As técnicas de circuito visavam principalmente circuitos que oferecessem o máximo em termos de desempenho por um lado [NN99, NN02], e baixo consumo por outro [CB95, Yea98], sendo que o ideal era sempre a conjugação das duas características.

Em relação às arquiteturas, principalmente no projeto de processadores, começou a se tornar mais comum o emprego de técnicas até então utilizadas somente em computadores de grande porte. Tornou-se muito mais comum o emprego de arquiteturas superescalares, grandes *trace caches*, estações de reserva, unidades funcionais com *pipelines* profundos, *data caches* no próprio chip, execução fora de ordem, especulativa e etc [PPE<sup>+</sup>97, Sim97]. De certa forma isso já era previsível, em 89 [GGPY89] comparava a evolução dos microprocessadores com a dos *mainframes*, e previa que o desempenho deles iria superar o dos *mainframes* em poucos anos. Estava caracterizada dessa forma, a importância da arquitetura no projeto final como fator de competitividade.

Como resultado, a década de 90 foi caracterizada por uma explosão de tamanho e complexidade dos componentes integrados. Primeiro, os processadores, seguido pelos periféricos integrados que saltaram de centenas de milhares para dezenas de milhões de componentes por circuito integrado, graças principalmente ao emprego de arquiteturas cada vez mais sofisticadas. Entretanto, houve relativamente pouco avanço nas ferramentas de auxílio nesse tipo de desenvolvimento.

Veremos nas próximas seções um apanhado do que foi desenvolvido em termos de ferramentas de projeto de sistemas digitais desde meados dos anos 80, 90 até os dias de hoje.

Veremos o mais importante: que todas as ferramentas e metodologias apresentadas têm muito mais caráter de implementação do que de concepção, objetivo principal deste trabalho. Mesmo considerando as Linguagens de Descrição de *Hardware*, muito em moda atualmente, veremos suas limitações e dificuldades em relação ao aspecto de elaboração e concepção arquitetural de novos sistemas.

### 2.1.1 Compilação de Silício

Compilação de Silício é a transformação de uma descrição de alto nível de um dado sistema em *layout*. Entendemos por “descrição de alto nível”, qualquer descrição que esconda do usuário algum nível de detalhamento. Normalmente o processo de transformação possui várias etapas, e costuma-se associar a cada uma destas etapas um compilador correspondente. Portanto, podemos definir um compilador lógico para transformar uma descrição num conjunto de portas lógicas e flip-flops, ou um compilador de microestrutura para transformar um dado conjunto de instruções num conjunto de registradores, *buses* e unidades funcionais, e assim por diante.

Na figura 2.2 vemos um diagrama em Y, proposto por [Gaj88, DG90], uma clássica representação da compilação de silício. Nele cada um dos eixos representa os três domínios de descrição: o comportamental, o estrutural e o físico (ou geométrico). Ao longo dos eixos são representados os vários níveis de representação/descrição. A informação do nível torna-se cada vez mais abstrata a medida que nos afastamos do centro do diagrama. As ferramentas de projeto são representadas como arcos entre os eixos de representação, e denotam graficamente a informação que a ferramenta usa e qual informação é gerada pela ferramenta.

No domínio comportamental o interesse é o que o circuito faz, e não como é construído. Normalmente, o elemento é uma caixa preta contendo entradas e saídas e uma função descritiva do comportamento de cada saída em função das entradas e, eventualmente, do tempo. O eixo estrutural é a ponte entre os domínios comportamental e físico. O domínio físico ignora o máximo possível o que o circuito deveria fazer, trazendo para o silício a informação estrutural do projeto (projeto físico/geométrico).

As transformações do eixo comportamental para o estrutural são chamadas síntese e as transformações do eixo estrutural para o físico são chamadas de implementações físicas. Juntas, síntese e implementação, são chamadas de compilação de silício.

Figura 2.2: Diagrama em Y.

Na figura 2.2 estão representados quatro compiladores que seriam necessários num sistema de compilação de silício ideal. O compilador de sistema decompõe programas e algoritmos num conjunto de processos comunicantes. O compilador de processador decompõe cada processo num conjunto de componentes de microarquitetura ou módulos. Os compiladores de módulos geram *layouts* de arranjos regulares ou irregulares de células e finalmente os compiladores de células decompõem as células em portas, transistores e eventualmente num conjunto de polígonos que representam o desenho em silício do elemento sintetizado.

### 2.1.1.1 Compilação de Células

O compilador de células traduz a descrição comportamental da célula, geralmente um conjunto de equações booleanas, num *layout* de máscaras. Por células, estamos nos referindo a funções de um único bit, elementos de armazenamento (bits de memória), registradores, componentes microarquiteturais ou até circuitos com complexidade SSI ou MSI.

A síntese de *layout* de células é em geral uma tarefa bastante difícil. É uma prática comum simplificar o problema impondo uma série de restrições à arquitetura da implementação e às

Figura 2.3: Exemplo de síntese de células CMOS com *layout* restrito a uma única de transistores P e uma de transistores N. Em (a) vemos a especificação funcional de uma célula CMOS complexa e o esquema correspondente. Em (b) os *Euler Paths* correspondentes. Em (c) temos o *layout* simbólico, e em (d) o *layout* real.

dimensões do mesmo. Obviamente, isto restringe a qualidade do *layout*, mas isso é encarado como um compromisso entre a complexidade do compilador e a qualidade do projeto.

### 2.1.1.2 Compilação de Módulos

O compilador de módulos traduz o comportamento de um dado módulo num conjunto de células interconectadas. A descrição do comportamento do módulo pode ser dada de várias maneiras como um conjunto de equações booleanas ou uma especificação de características que podem ser usadas para criar um *template* para o módulo. Os módulos podem ser caracterizados pelo tipo de lógica que implementam, podem ser lógicas aleatórias ou módulos matriciais ou regulares.

Os módulos de lógicas aleatórias são usados normalmente para implementar funções de baixa hierarquia na arquitetura e são implementados em geral com PLAs, *standard cells* ou lógica customizada. A especificação comportamental de uma lógica aleatória geralmente não produz um *layout* ótimo, sendo comum adotar-se o procedimento de otimizar a descrição antes de proceder a qualquer tipo de síntese. A estratégia de otimização é composta pelas seguintes etapas: minimização, fatoração, mapeamento e otimização.

- **Minimização:** pela minimização procura-se gerar um conjunto mínimo de equações, na forma de soma-de-produtos a fim de minimizar assim o número de transistores.

- **Fatoração:** na fatoração podemos reduzir ainda mais o número de transistores fatorando as equações em busca de elementos comuns. Essa técnica entretanto pode diminuir o desempenho do circuito, pois introduz níveis adicionais à lógica.

- **Mapeamento:** Algumas tecnologias possuem um conjunto pré estabelecido de células para implementar lógica aleatória. Todos os procedimentos posteriores de implementação devem levar em consideração esse conjunto, portanto as descrições intermediárias devem estar “mapeadas” nos elementos dessa tecnologia.

- **Otimização:** Finalmente um último passo de otimização com todos os elementos considerados. Desde que podem existir vários tipos de portas lógicas na biblioteca de células, otimizamos a lógica substituindo grupos de portas pelos correspondentes mais apropriados, através de um procedimento que envolve certas regras e algoritmos

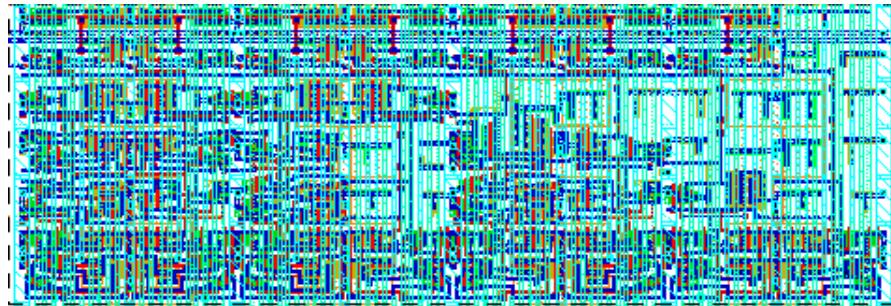

Figura 2.4: Exemplo de implementação de lógica aleatória em *standard cells*.

Figura 2.5: Exemplo de módulo regular, somador de 8 bits.

especiais. Uma boa referência sobre o processo de minimização/otimização multi-nível pode ser encontrada em [BHSV90].

Módulos matriciais ou regulares são comumente elementos microarquiteturais que desempenham funções específicas. Exemplos desses módulos são ROMs, RAMs, banco de registradores, unidades funcionais, contadores e *data paths*. Um módulo regular é definido por um *template* e um conjunto de células que ocupam posições pré-definidas neste *template*. A especificação de um módulo regular consiste na definição das células e respectiva posição de forma a implementar a funcionalidade desejada. A figura 2.5 é um exemplo desse caso, a figura 2.4 por outro lado apresenta uma versão mais genérica de implementação de lógica aleatória que chamamos *standard cells*.

Num módulo regular a interface de células é feita por simples justaposição, devendo o projetista confiar que qualquer combinação de células é possível. Dessa forma, nenhuma regra de projeto é violada na implementação de uma determinada função. O circuito é

correto por construção.

Além da geração de *layout* os geradores de módulos também podem gerar modelos para a interação com outras ferramentas como: símbolos para diagramas esquemáticos, modelos para simuladores diversos, geometrias para *Floor planners*, etc.

### 2.1.1.3 Compilação de Processador

Compilação de processador é o nome do processo que traduz uma descrição comportamental abstrata de um elemento processador num conjunto de elementos arquiteturais como: registradores, unidades funcionais e etc. O termo mais usado para esta classe de ferramentas é “Síntese de Alto Nível” e será explorada com mais detalhe na seção 2.1.2.

Essa descrição comportamental consiste de uma caixa preta com canais de entrada e saída, e uma função de transformação das entradas para as saídas. Descrição que pode ser feita, em princípio, por qualquer linguagem de programação. Entretanto para a maioria das linguagens precisa-se adotar um modelo simplificado uma vez que essas linguagens não possuem as noções de tempo, atraso, desempenho ou conectividade, normalmente necessários para uma descrição de *hardware*. Somente a ordem de execução é especificada usando as estruturas de controle da linguagem e instruções seqüenciais. Linguagens de descrição de *Hardware* específicas para simulação e documentação de sistemas digitais foram concebidas, podendo ser usadas também para propósitos de síntese; entretanto, veremos na seção 2.1.3 que nem sempre uma semântica apropriada para simulação é também apropriada para síntese de *hardware*.

A fim de simplificar o processo de síntese, a maioria dos compiladores de processadores assumem arquiteturas de *hardware* bem comportadas e definidas com alvo da síntese. Um modelo comum pode ser visto na figura 2.6. Nele, considera-se o sistema como um conjunto de elementos de processamento (PE, *Processing Elements*) conectados. Cada PE consiste de uma unidade de controle (CU, *Control Unit*), e um *datapath* (DP). As unidades de controle são implementadas genericamente como máquinas de estados finitos, contendo portanto um registrador de armazenamento do estado interno e uma lógica de geração dos estados futuros, sinais de controle e comunicação com outros PEs. *Datapaths*, por sua vez consistem de unidades de armazenamento e unidades funcionais que são conectadas por intermédio de *buses*. Os elementos de armazenamento podem ser registradores, contadores, banco de regis- tra-

dores e memórias; enquanto, unidades funcionais são ALUs, registradores de deslocamento, multiplicadores e etc.

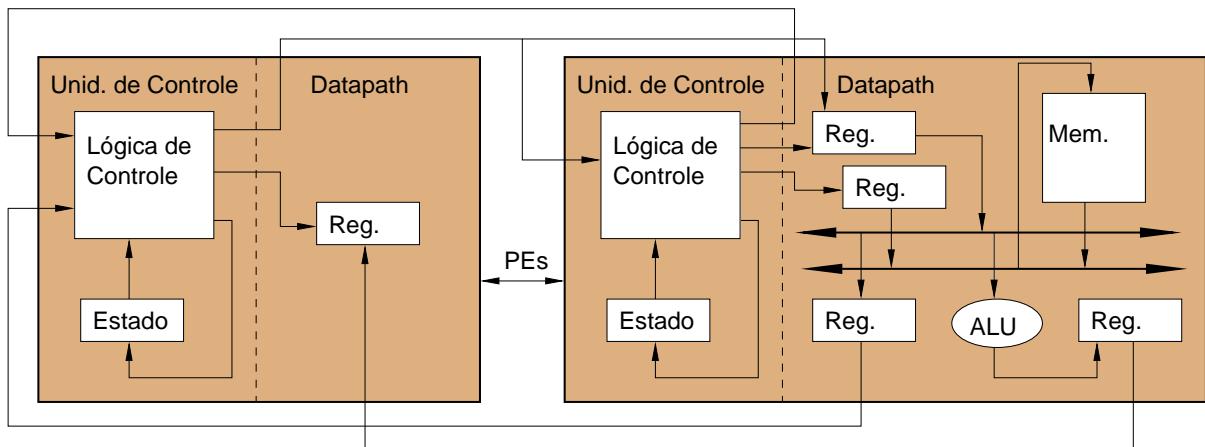

Figura 2.6: Modelo de Elementos de Processamento, PEs.

O processo compilação (ou síntese) consiste no mapeamento de construções da linguagem comportamental em componentes arquiteturais. Este processo é chamado genericamente de *binding*. Variáveis são alocadas em elementos de armazenamento (registradores) ou de conexão (sinais ou *buses*), é o *register binding*. Operadores, por sua vez, transformam-se em unidades funcionais, é o *unit binding*. Quando variáveis são modificadas, deve-se estabelecer conexões para ligar registradores a unidades funcionais para trazer a variável até a unidade correspondente e levá-la de volta até o registro apropriado, isto é o *connection binding*. É preciso também converter as estruturas de controle da linguagem de descrição – como *loops* e desvios – em operações seqüenciais das unidades de controle no *hardware* sintetizado. Cada operação deve por sua vez estar associada a um *time step* ou estado. Este processo chama-se *state binding*.

A alocação de elementos arquiteturais não cobre toda a gama de possibilidades de geração de *hardware* uma vez que muitas estruturas diferentes podem ser concebidas implementando a mesma funcionalidade. A escolha de qual estrutura será utilizada é dada pelas restrições de projeto: desempenho, área e consumo de potência. Baseado nestas restrições, o processo de alocação de recursos cria uma representação intermediária chamada de grafo de fluxo de dado/controle (*control/data flow graph*), que elimina dependências desnecessárias da linguagem de entrada, e pode ser facilmente manipulada para se estabelecer a estrutura mais apropriada. Veremos mais detalhes deste assunto na seção 2.1.2.

### 2.1.1.4 Sistema de Projeto

Um sistema de projeto ideal baseado em compilação de silício combina os processos apresentados nas seções anteriores, ou seja, deve utilizar os compiladores de processadores (síntese de alto nível) e compiladores de módulos e células. O usuário descreve o circuito numa linguagem de alto nível e deixa que o sistema se encarregue de gerar o *layout* automaticamente.

Na figura 2.7, é apresentado um sistema de projeto como foi proposto por [DG90, Gaj88].

Figura 2.7: Projeto de sistemas baseados em Compilação de Silício.

Podemos ver pela figura que o sistema pode ser especificado tanto no nível comportamental quanto estrutural, a ponte é feita na etapa de síntese. O bloco de tecnologia contém toda informação relevante ao processo de fabricação e regras de projeto, usadas para a geração do *layout*. Além do *layout*, o compilador de silício gera também modelos de tempo e modelos lógicos para cada elemento da estrutura. Em seguida, ferramentas de *placement* e *routing* se encarregam da composição final. Vemos também que em quase todas as etapas estão presentes editores que provêm acesso interativo às atividades do compilador, permitindo ao usuário interferir no resultado final do processo.

O sistema de projeto deve compreender também um conjunto de ferramentas de suporte,

que costumam pertencer a um dos seguintes grupos: ferramentas de verificação, análise e otimização.

- **Verificação:** ferramentas de verificação constatam a correção das descrições comportamental e estrutural. Geralmente constituem-se de simuladores de vários tipos como funcional, lógico, elétrico e de falha. Uma outra forma de verificação baseada em provas matemáticas – chamada verificação formal será abordada com mais detalhe na seção 2.1.4.

- **Análise:** as ferramentas de análise são usadas para determinar ou pelo menos estimar a qualidade geral do *layout* sintetizado. São freqüentemente os analisadores de *timing* que determinam o atraso entre portas ou elementos. Através do levantamento desses atrasos podemos determinar caminhos críticos que, por sua vez, determinam o desempenho máximo do sistema. Outra análise comum é a análise de testabilidade. Por essa, são calculadas a controlabilidade e observabilidade do circuito. A controlabilidade é uma medida que determina o grau de dificuldade de se controlar um nó do circuito, enquanto a observabilidade mede a dificuldade do mesmo ser observado. Com base nessas medidas é possível planejar as estratégias de teste para o sistema.

- **Otimização:** O *layout* produzido pela compilação de silício nem sempre é ótimo, mas é possível melhorá-lo sem comprometer as outras restrições de projeto através das ferramentas de otimização. No nível geométrico podemos citar as ferramentas de compactação, os PLA *folders*, *resizing* de transistores e etc. Nos níveis intermediários otimizadores de qualidade auxiliam os processos de transformação de descrições.

## 2.1.2 Síntese de Alto Nível

Como vimos na seção 2.1.1.3, a síntese de alto nível tem recebido diferentes nomes ao longo do tempo. “Compilação de Processador”, “Síntese Comportamental” ou “de Alto Nível”, todas se referem ao processo de mapeamento de uma descrição comportamental, feita numa linguagem de descrição de *hardware*, numa descrição estrutural ou malha interconectada de elementos arquiteturais, também chamada descrição RTL<sup>†</sup>. Veremos a seguir alguns fundamentos das técnicas utilizadas neste campo de pesquisa.

### 2.1.2.1 Representação Interna

Os sistemas de síntese de alto nível (HLS - *High Level Synthesis*) são incapazes de operar diretamente sobre as descrições de *hardware*, ao invés disso, utilizam uma representação interna onde são aplicadas as transformações que tornam a descrição comportamental mais próxima da RTL. Esta representação é conhecida como grafos de fluxo de dados e controle, CDFG - *control and data flow graphs*, e consistem numa representação melhor estruturada da *parse-tree* gerada pela etapa de *parsing* da linguagem.

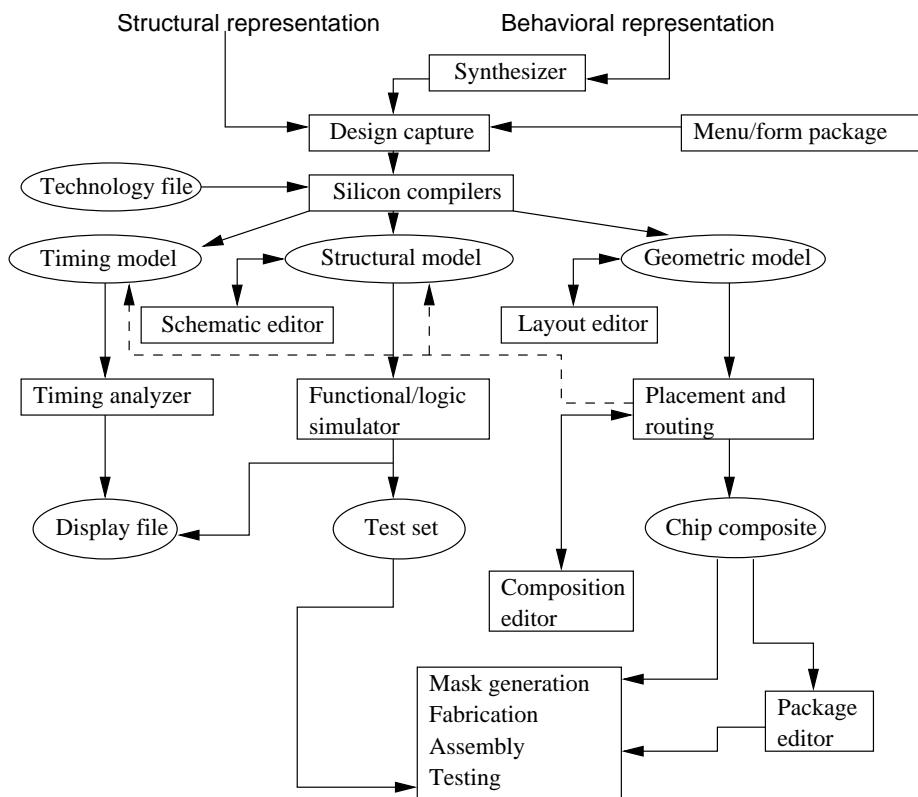

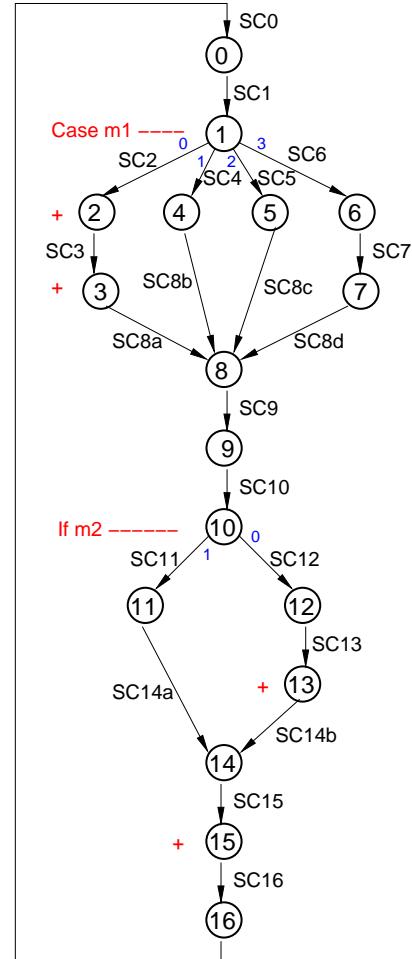

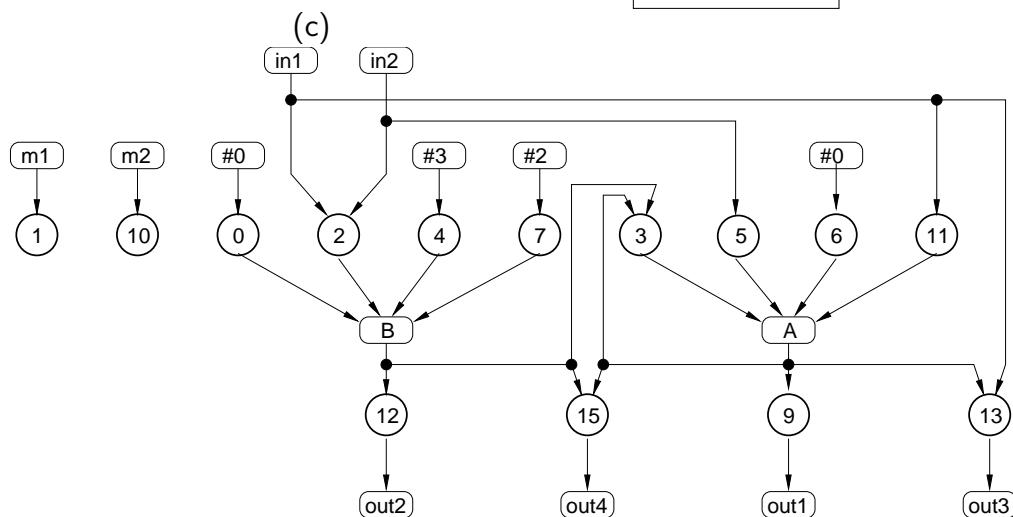

CDFGs existem em muitas formas diferentes. Em [Ber02] nos é dado um exemplo que reproduzimos na figura 2.8, na qual é apresentada uma representação que destaca o controle dos dados. Essa representação é mais simples de ser compreendida sem grandes explicações e não apresenta desvantagens em relação às representações combinadas. O grafo de fluxo de controle (CFG - *Control Flow Graphs*) representa o seqüenciamento das operações descritas na linguagem de especificação, incluindo operações de reordenamento, expansão de *loops* e desdobramentos (*unfolding*). O grafo de fluxo de dados, por sua vez, representa a interdependência entre dados, operações e valores. Note-se que, para cada nó no grafo de fluxo de dados, existe um correspondente no fluxo de controle; porém, o inverso não é verdadeiro. Os nós que representam os *ends* da linguagem não têm correspondentes no DFG.

### 2.1.2.2 Operações Básicas

Como foi dito na seção 2.1.1.3, o modelo-alvo das operações de síntese consiste de unidades de processamento (PE), exemplificadas na figura 2.6. Essas unidades nada mais são que máquinas de estados finitos associadas a *datapaths*, ou FSMD (*Finite State Machine with Datapath*). Em princípio, da análise dos grafos de fluxo de dados, podemos derivar os *datapaths* e, da análise dos fluxos de controle, derivamos a máquina de controle. Evidentemente, os problemas da vida real mostram-se muito mais complicados do que gostaríamos que fossem.

O processo de síntese de alto nível deve-se balizar em parâmetros de projeto, como por exemplo: custo, desempenho, consumo de potência e etc. Esses parâmetros devem guiar o processo de síntese, tornando-o bastante complicado, uma vez que a solução trivial raramente satisfaz aos requisitos de projetos. Dessa forma, os sistemas de HLS adotaram estratégias de implementação que permitiram a exploração destes requisitos durante o processo de síntese.

(a)

```

Entity bde is

port ( clock: in bit;

in1, in2, m1: in integer range 0 to 3;

m2: in boolean;

out1, out2, out3, out4: integer range 0 to 3 );

end bde;

Architecture behavior of bde is

begin

Process

Variable A, B: integer range 0 to 3;

Begin

Wait until not clock'stable and clock='1';

B := 0; -- 00

Case (m1) is

when 0 => B := in1 + in2; -- 02

A := A + B; -- 03

when 1 => B := 3; -- 04

when 2 => A := in2; -- 05

when 3 => A := 0; -- 06

B := 2; -- 07

end Case;

out1 <= A; -- 09

If (m2)

then A := in1; -- 011

else out2 <= B; -- 012

out3 <= A + in1; -- 013

end If;

out4 <= A + B; -- 015

end Process;

end behavior;

```

(b)

(c)

Figura 2.8: (a) Descrição VHDL comportamental. (b) Grafo de fluxo de controle. (c) Grafo de fluxo de dados.

Em geral um sistema de HLS pode ser dividido nas seguintes etapas [Gov95]:

1. **Compilação:** nesta fase a descrição comportamental é analisada e traduzida para uma representação intermediária (CDFGs) onde serão aplicadas as futuras transformações.

2. **Particionamento:** nesta fase faz-se o particionamento do sistema quando necessário, para efeito de redução do problema a ser analisado e/ou redução da complexidade.

3. **Scheduling:** o processo de *scheduling* consiste na divisão da representação interna em estados de controle de forma a possibilitar o seu futuro mapeamento numa máquina de estados de controle. Essa constitui a fase mais importante da síntese. Sobre ela, pode-se adotar estratégias que levam em consideração os requisitos de projeto (*constraints*).

Os algoritmos de *scheduling* podem por sua vez serem caracterizados como:

- **Básicos:** são algoritmos baseados mais em bom senso do que em requisitos propriamente ditos. Eles também constituem o ponto de partida de várias outras estratégias. São elas:

- (a) **ASAP:** “*As Soon As Possible*”, determina a mais rápida alocação de operações por estados possível, consequentemente o menor número de passos de controle.

- (b) **ALAP:** “*As Late As Possible*”, essencialmente oposto ao anterior produzindo a mais lenta alocação “operações/estados” e o maior número de passos de controle.

- **por Restrições Temporais:** algoritmos por restrições temporais também são chamados de “abordagem por número de passos fixos”. Em geral, partem de uma solução ASAP/ALAP e então aplicam uma das seguintes técnicas:

- (a) **Programação Matemática:** caracterizada pelo método de ILP (*Integer Linear Programming*) que procura otimizar a solução através de buscas, *backtracking*. Esse método apresenta altíssima complexidade, execução demorada e solução ótima.

- (b) **Heurísticas Construtivas:** caracterizada pelo método FDS (*Force Directed Scheduling*), este método procura distribuir igualmente as operações de mesmo tipo sobre o conjunto de passos de controle. É o mais popular – complexidade baixa, execução rápida e solução quase ótima.

- (c) **Refinamento Iterativo:** caracterizada pelo método IR (*Iteractive Rescheduling*), consiste em modificar uma alocação avaliando o custo da nova implementação. A qualidade da solução depende da alocação inicial, a complexidade é alta e o tempo de execução, médio.

- **por Restrições de Recursos:** são indicados quando há restrição em área de silício. Dois métodos se destacam:

- (a) ***Scheduling* Baseado em Listas:** Este método mantém uma lista de prioridades para operações “prontas”, ordenadas de acordo com uma função de prioridade. Operações “prontas” são operações cujos predecessores já foram alocados. Uma vez que uma operação da lista é alocada num passo de controle, muitas outras passam a ser “prontas” e devem ser incluídas na lista ordenada. O sucesso do *scheduler* irá depender da função de prioridade adotada. A complexidade computacional deste método é alta, porém produz resultados quase sempre ótimos. É mais lento que o método FDS.

- (b) ***Scheduling* com Listas Estáticas:** apesar de lidar com listas, este método difere do anterior tanto nos meios de alocação quanto na forma de ordenar as listas. O método parte de uma solução ASAP e uma ALAP para obter o menor e o maior número de passos de controle (LCS - *Least Control Step* e GCS - *Greatest Control Step*, respectivamente), para cada operação. O algoritmo usa então essas designações para ordenar uma grande lista única que será usada como guia para a alocação. Toda vez que o limite de recursos é alcançado, a alocação avança para um passo de controle posterior. Este método é um pouco mais rápido que o anterior e também produz bons resultados.

- **Outros Métodos:** Além dos métodos apresentados existem vários outros que não se enquadram nas categorias anteriores. Em particular, dois métodos se destacam, são eles:

- (a) ***Simulated Annealing*:** por este método, o cronograma de alocação operação/estado é representado por uma tabela bidimensional de passos de controle por unidades funcionais, então o problema é convertido a um problema de *placement*, onde as posições da tabela são preenchidas com as operações. Come-

çando com uma solução inicial, o algoritmo modifica iterativamente a solução calculando o custo da modificação. Uma modificação é aceita, associada a uma certa probabilidade, de forma que o espaço solução possa ser vasculhado a fim de alcançar os mínimos. Apesar de robusto, esse método consome longos períodos de execução.

- (b) *Path-Based Scheduling*: *path-based scheduling* procura minimizar o número de passos de controle necessários para executar o caminho crítico do CDFG. Todos os caminhos de execução são extraídos e alocados independentemente. Ao final, os diferentes caminhos são combinados para gerar a solução.

4. **Alocação**: esta fase trabalha em relação íntima com a fase de *scheduling*, e consiste no particionamento da representação intermediária com respeito ao espaço (recursos de *hardware*), também conhecido como mapeamento espacial. Ela também determina o esquema de *clock*, hierarquia de memória e estilo *pipeline*. Para satisfazer a todos estes requisitos, a alocação deve determinar a área exata e o desempenho das unidades alocadas. Uma aproximação do custo e desempenho pode ser dado pelo número de unidades funcionais e pelo número de passos de controle. Ao invés de buscar automaticamente através de todo o espaço de projeto, a maioria das ferramentas de HLS atuais permitem algum grau de interação do usuário, oferecendo métricas para auxiliar o projetista a fazer a melhor escolha.

5. **Binding**: Esta fase associa cada operação e acesso a memória, em cada passo de controle, a um elemento de *hardware*. Um dado recurso, como unidade funcional, armazenamento ou interconexão pode ser compartilhado por diferentes operações desde que sejam mutuamente exclusivas[GR94]. A fase de *binding* consiste de três sub-tarefas, de acordo com o tipo de unidade:

- *Storage Binding*, associa variáveis a unidades de armazenamento. Unidades de armazenamento podem ser de muitos tipos, incluindo registradores, banco de registradores e/ou memória. Duas variáveis que existem em passos de controle diferentes podem compartilhar o mesmo registrador. Duas variáveis que não são acessadas simultaneamente podem, num dado estado, ser associadas ao mesmo *port* ou memória.

- *Functional Unit Binding*, associa cada operação, num dado passo de controle, a uma unidade funcional. Uma unidade funcional ou estágio de *pipeline* só pode executar uma única operação por ciclo de relógio.

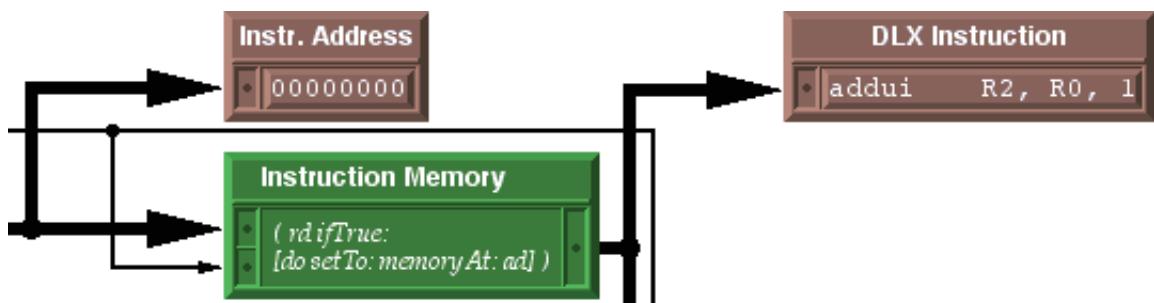

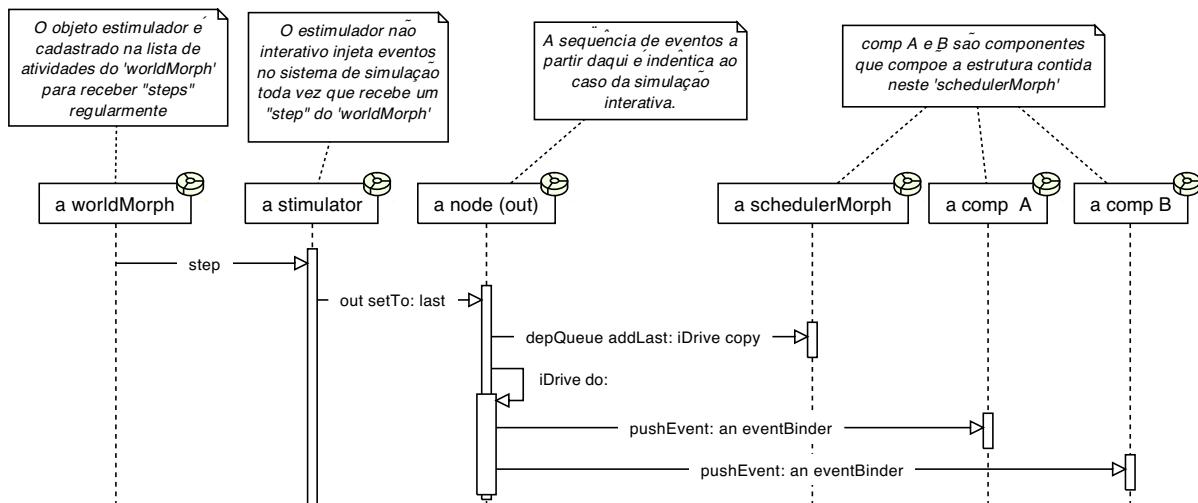

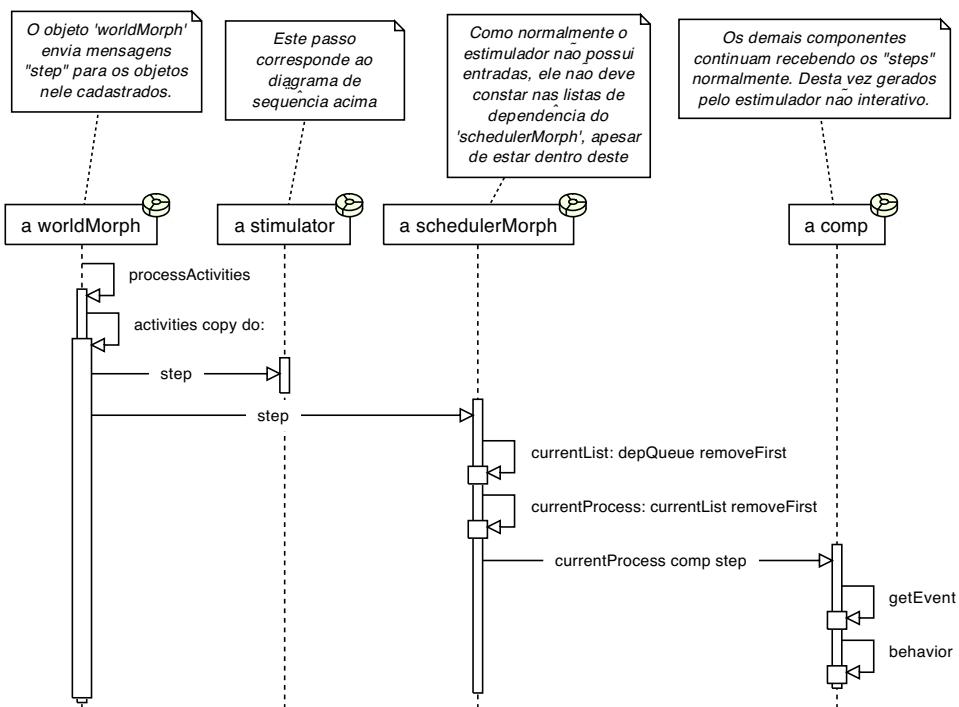

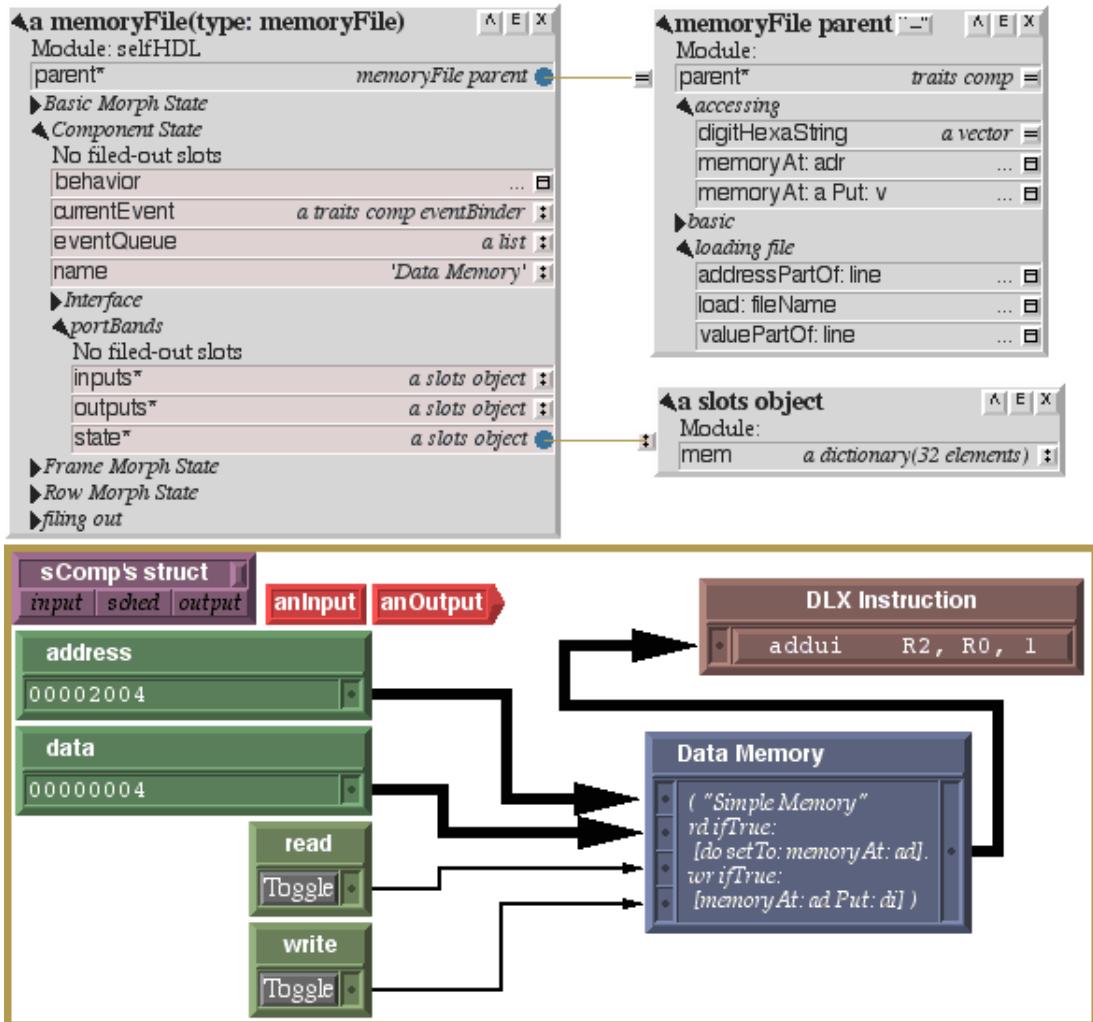

- *Interconnection Binding*, associa unidades de interconexão como multiplexadores ou barramentos para cada transferência de dados entre *ports*, unidades funcionais ou de armazenamento.